023 低功耗设计

Posted SilentLittleCat

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了023 低功耗设计相关的知识,希望对你有一定的参考价值。

功耗源

- 浪涌电流:器件上电时产生的最大瞬时输入电流,也称启动电流

- 静态功耗:关断主电源或系统进入待机模式下产生的功耗,包含晶体管漏电流导致的功耗

- 动态功耗:门电路输出切换时,由逻辑转换引起的功耗

P d y n a m i c = S C L V d d 2 f c l k P_dynamic=SC_LV_dd^2f_clk Pdynamic=SCLVdd2fclk

- C L C_L CL:门寄生电容

- S S S:每个时钟通过整个电路的平均转换次数

- f c l k f_clk fclk:时钟频率

- V d d V_dd Vdd:供电电压

P t o t a l = P d y n a m i c + P s t a t i c P_total=P_dynamic+P_static Ptotal=Pdynamic+Pstatic

典型应用中动态功耗占到总功耗的80%

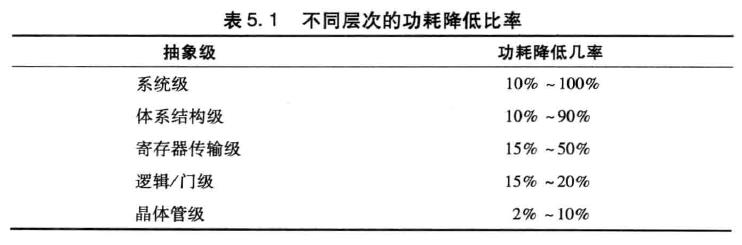

各设计抽象层次降低功耗

系统级低功耗技术

片上系统

对于纳米级高端芯片,I/O使用比芯片内部逻辑更高的电压供电(典型为3.3V),使得其占到总功耗50%以上。如果系统包含多块芯片,芯片间连线将消耗大量功耗。

硬件/软件划分

通信算法具有高度递归性质,递归模块可能占整体系统很小一部分,但能显著降低功耗

低功耗软件

- 避免使用复杂原语

- 使用中断替代高频轮询

- 循环合并

处理器

- 采用适合要求的数据宽度的处理器

- 利用微处理器,协处理器、DSP进行数据处理

体系结构级低功耗技术

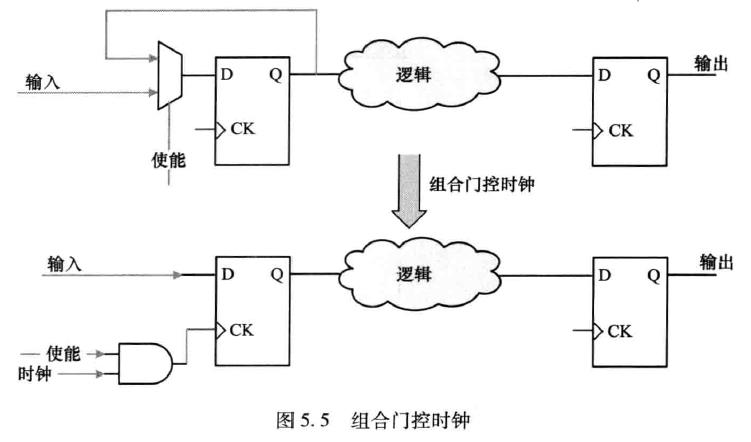

高级门控时钟

动态电压频率调节

DVFS(Dynamic Voltage/Frequency Scaling)

缓存

对数FFT体系替代线性系统

异步(无时钟)设计

电源门控

多阈值电压

多点压供电

储存器电源门控

典型SoC中,SRAM消耗了总功耗的1/3,其他部分由时钟树和随即逻辑消耗掉

寄存器传输级降低功耗

状态机编码解码

格雷码最适合低功耗设计

二级制数表示法

独热码多路器

资源共享

行波计数器

总线反转

寄存器级低功耗奇数

工艺水平

版图优化

衬底偏压

较小氧化层厚度

《硬件架构的艺术——数字电路的设计方法与技术》[印度] Mohit Arora

以上是关于023 低功耗设计的主要内容,如果未能解决你的问题,请参考以下文章