AXI协议:AMBA总线介绍,AXI概念与背景介绍,AXI协议特点与功能

Posted 呆呆象呆呆

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了AXI协议:AMBA总线介绍,AXI概念与背景介绍,AXI协议特点与功能相关的知识,希望对你有一定的参考价值。

1 AMBA总线介绍

AMBA(Advanced Microcontroller Bus Architecture)总线规范是 ARM 公司提出的总线规范,被大多数 SoC 设计采用,下面让我们按照其发布版本来认识一下它。

- AMBA版本1规范定义:

- ASB(Advanced System Bus)

- APB(Advanced Peripheral Bus);

- AMBA版本2规范定义:

- AHB(Advanced High-performance Bus)

- ASB

- APB

- AMBA版本3规范定义:

- AXI v1.0(Advanced Extensible Interface)

- AHB-Lite v1.0

- APB v1.0

- ATB v1.0(Advanced Trace Bus)

- AMBA版本4规范定义:

- ACE(AXI Coherency Extensions)

- ACE-Lite

- AXI4

- AXI4-Lite

- AXI4-Stream v1.0

- APB v2.0

- ATB v1.1

- 最新一代的AMBA4规范的目标如下:

- 适合高带宽和低延迟设计

- 在不使用复杂的桥接方式下,允许更高频率的操作

- 满足普遍情况下的元件接口要求

- 适用于高初始访问延迟的存储器控制器

- 为互联结构的实现提供灵活性

- 向下兼容已有的AHB和APB接口。

一些协议的简单介绍

AHB 用于高性能、高时钟频率的系统结构,具有流水线操作、多个总线主设备、猝发传输、分割交易等特性。

APB 提供一个低功耗的接口,降低了接口的复杂性;用于在低带宽和不需要高性能总线的外部设备上;属于非流水线结构,所有的信号仅与时钟上升沿相关,锁存的地址和控制。

AXI4 协议基于突发式传输机制,具有独立的地址/控制和数据通道;使用字节选通,支持非对齐的数据传输;只有开始地址的猝发交易;独立的读和写数据通道;使能低成本的直接存储器访问DMA传输;能发出多个未解析的地址;完成无序交易;容易添加寄存器切片,满足时序收敛要求。

2 AXI概念与背景介绍

AXI,是 Xilinx 从 6 系列的 FPGA 开始引入的一个接口协议,主要描述了主设备和从设备之间的数据传输方式。

AXI 是 ARM 公司提出的AMBA的一个部分,是一种高性能、高带宽、低延迟的片内总线,也用来替代以前的 AHB 和 APB 总线。AXI 技术丰富了现有的AMBA标准内容,满足超高性能和复杂的片上系统(SoC)设计的需求。

-

第一个版本AXI(AXI3)包含在 2003年发布的 AMBA3.0 中

-

第二个版本AXI(AXI4)包含在 2010年发布的 AMBA4.0 中

理解方式,你开车要开在路上,现在AXI就是一条具有标准的路,规定好了交通规则比如靠右行驶,怎么下高速,怎么去到别的城市。

3 特点

- 具有独立的地址/控制通道和数据通道,信息流只以单方向传输,简化时钟域间的桥接,减少门数量。当信号经过复杂的片上系统时,减少延时。独立的地址和数据通道。地址和数据通道分开,能对每一个通道进行单独优化,可以根据需要控制时序通道,将时钟频率提到最高,并将延时降到最低。

- 基于突发式传输机制(burst)处理(transaction),并且只给出来一个起始地址(start-address)。 支持多项数据交换。通过并行执行猝发操作,极大地提高了数据吞吐能力,可在更短的时间内完成任务,在满足高性能要求的同时,又减少了功耗。

- 将写数据(write data channel)和读数据通道(read data channel)分离开来,请注意都是针对数据通道而言,并且可以提供一个低功耗的直接存储器访问(direct memory acess)

- 高性能(高速,高频率,高带宽,低延迟)的数字系统

- 通过字节选通的方式(byte strobe),支持非对齐数据传输(unaligned data transfer)

- 支持处理多个未解决的地址(support for issuing multiple outstanding addresses)

- 支持无序的处理(support for out-of-order transaction )

- 提供寄存器进行一些时序终止操作。

- 可以和一系列复杂接口的元器件设备匹配,可以给很多片上结构提供互联

- 可以反向兼容 AHB 和 APB 接口

4 AXI协议具体干了什么:链接主从设备

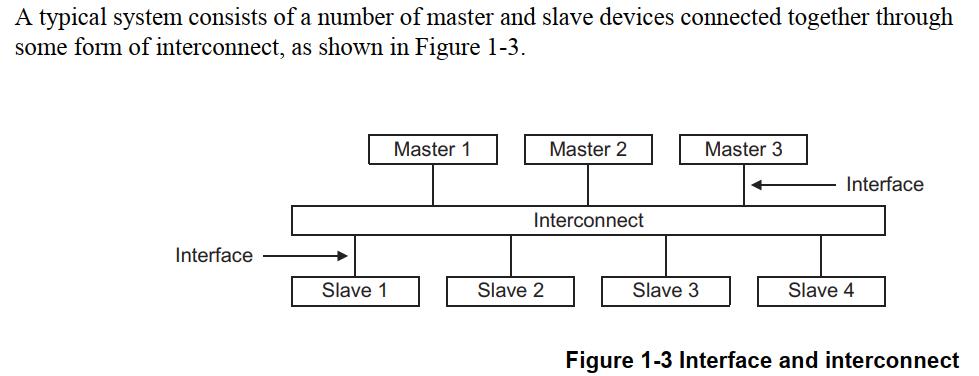

读和写操作其实都是是对应于总线链接两边的设备而言的,也就是我们常说的主设备(master)和从设备(slave)。

master/slave链接示意图。

AXI 协议主要就是对如下情况的接口进行定义:

- 在master和interconnect之间

- 从slave和interconnect设备之间

- 在master和slave之间

主设备和从设备分别指 AXI 两边连接的东西

以上是关于AXI协议:AMBA总线介绍,AXI概念与背景介绍,AXI协议特点与功能的主要内容,如果未能解决你的问题,请参考以下文章