配置STA环境

Posted KuoGavin

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了配置STA环境相关的知识,希望对你有一定的参考价值。

文章目录

本章节介绍了如何为静态时序分析配置环境。正确的约束对于分析STA结果很重要,只有准确指定设计环境,STA分析才能够识别出设计中的所有时序问题。STA的准备工作包括设置时钟、指定IO时序特性以及指定伪路径和多周期路径。在继续学习下一章的时序验证之前,请务必全面了解本章节。

7.1 什么是STA环境(What is the STA Environment)

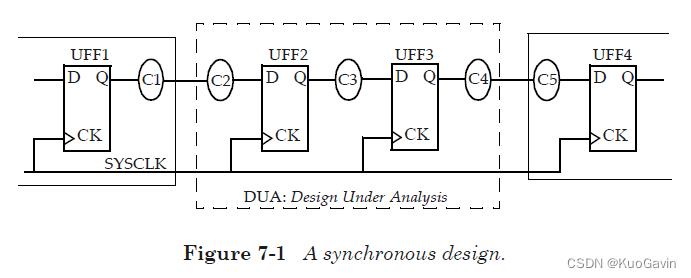

大部分数字设计是同步的,从前一个时钟周期计算出的数据在时钟有效沿上被锁存在触发器中。考虑图7-1中的典型同步设计。假定待分析设计(Design Under Analysis, DUA)会与其他同步设计交互。这意味着DUA从一个时钟触发器获取数据并将数据输出至DUA外的另一个时钟触发器。

为对这种设计执行STA,需要指定触发器的时钟,且需要进入和退出设计的所有路径的时序约束。

图7-1中的例子假定这里只有一个时钟和 C 1 C1 C1, C 2 C2 C2, C 3 C3 C3, C 4 C4 C4,和 C 5 C5 C5表示组合逻辑块,其中 C 1 C1 C1和 C 5 C5 C5在设计之外。

在一个典型设计中,可以有多个时钟,且存在多个路径从一个时钟域到另一个时钟域。以下部分描述了在这个场景下如何配置STA环境。

7.2 指定时钟(Specifying Clocks)

定义一个时钟,需要以下信息:

- i i i. 时钟源(Clock source):可以是设计的一部分,或是设计内单元的引脚(通常是时钟生成逻辑的一部分);

- i i ii ii. 周期(Period):时钟的时间周期;

- i i i iii iii. 占空比(Duty cycle):高电平持续时间(正相位)和低电平持续时间(负相位);

- i v iv iv. 边沿时间(Edge time):上升沿和下降沿的时刻;

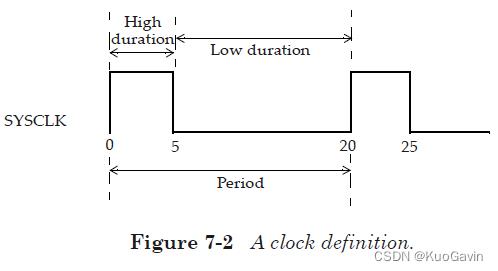

基本定义如图7-2所示。通过定义时钟,所有的内部时序路径(所有触发器到触发器的路径)均受到约束;这意味着所有的内部路径可仅使用时钟约束(clock specification)来分析。时钟约束指定触发器到触发器的路径必须占用一个周期。我们将介绍占用一个周期时间的要求怎样可以放宽。

这里有一个基本时钟约束/规范(specification和contraint在SDC规格中是同义词):

create_clock \\

-name SYSCLK \\

-period 20 \\

-waveform 0 5 \\

[get_ports2 SCLK]

该时钟名为SYSCLK,并在端口SCLK上定义。SYSCLK的周期指定为

20

20

20个单位,如果未指定,默认时间单位为纳秒(通常,时间单位会在技术库中进行指定)。waveform中的第一个自变量指定出现上升沿的时刻,第二个自变量指定出现下降沿的时刻。

waveform选项中可以指定任意数量的边沿。但是,所有边沿必须在一个周期内。边沿时刻从零时刻之后的第一个上升沿开始,然后是下降沿,然后再是上升沿,以此类推,这意味着waveform列表中的所有时刻值必须单调增加。

-waveform time_rise time_fall time_rise time_fall ...

另外,必须指定偶数个边沿时刻。waveform选项将指定一个时钟周期内的波形,然后不断重复。如果未指定任何waveform选项,则默认值为:

-waveform 0, period/2

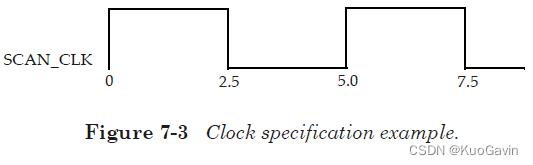

如下图7-3所示是一个没有指定waveform选项的时钟约束的示例:

create_clock -period 5 [get_ports SCAN_CLK]

在此约束中,由于未指定-name选项,因此时钟的名称与端口的名称相同,即SCAN_CLK。

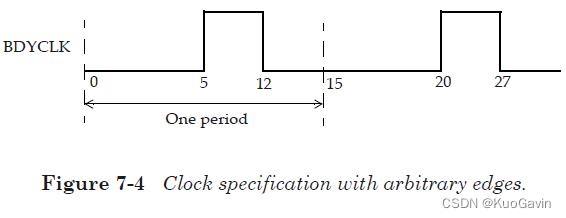

下图7-4是时钟约束的另一个示例,其中波形的边沿在一个周期的中间位置。

create_clock -name BDYCLK -period 15 \\

-waveform 5 12 [get_ports GBCLK]

所创建时钟的名字为BDYCLK且其被定义在端口GBLCLK上。实际上,将时钟名和端口名保持一致最好。

以下是更多的时钟约束示例:

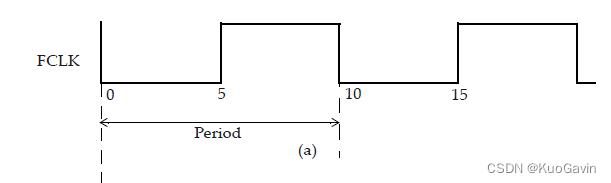

# See Figure 7-5(a):

create_clock -period 10 -waveform 5 10 [get_ports FCLK]

# Creates a clock with the rising edge at 5ns and the

# falling edge at 10ns.

# See Figure 7-5(b):

create_clock -period 125 \\

-waveform 100 150 [get_ports ARMCLK]

# Since the first edge has to be rising edge,

# the edge at 100ns is specified first and then the

# falling edge at 150ns is specified. The falling edge

# at 25ns is automatically inferred.

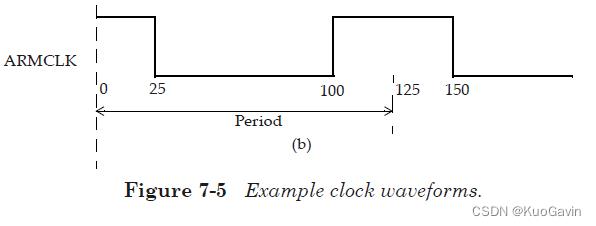

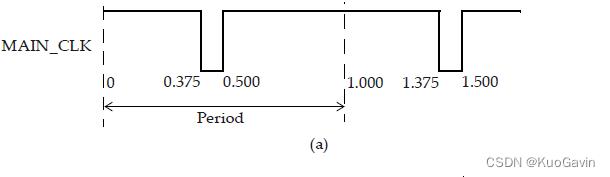

# See Figure 7-6(a):

create_clock -period 1.0 -waveform 0.5 1.375 MAIN_CLK

# The first rising edge and the next falling edge

# is specified. Falling edge at 0.375ns is inferred

# automatically.

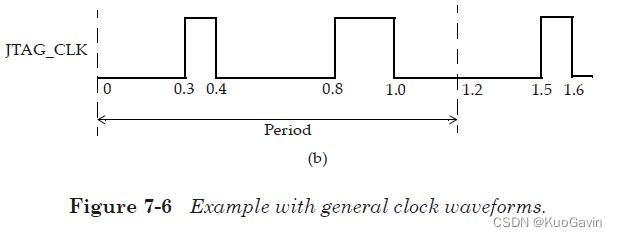

# See Figure 7-6(b):

create_clock -period 1.2 -waveform 0.3 0.4 0.8 1.0 JTAG_CLK

# Indicates a rising edge at 300ps, a falling edge at 400ps,

# a rising edge at 800ps and a falling edge at 1ns, and this

# pattern is repeated every 1.2ns.

还有一些时钟约束如下:

create_clock -period 1.27 \\

-waveform 0 0.635 [get_ports clk_core]

create_clock -name TEST_CLK -period 17 \\

-waveform 0 8.5 -add [get_ports ip_io_clk[0]]

# The -add option allows more than one clock

# specification to be defined at a port.

除了上述属性外,还可以在时钟源处指定过渡时间/压摆(transition_time/slew)。在某些情况下,例如顶层的输入端口或某些PLL的输出端口,工具无法自动计算出过渡时间。在这种情况下,在时钟源处显式地指定过渡时间很有用,这可以使用set_clock_transition命令来指定。

set_clock_transition -rise 0.1 [get_clocks CLK_CONFIG]

set_clock_transition -fall 0.12 [get_clocks CLK_CONFIG]

这个约束仅适用于理想时钟,一旦构建了时钟树就将其忽略,因为此时将会使用时钟引脚上的实际过渡时间。如果在输入端口上定义了时钟,也可以使用set_input_transition命令(参见7.7节)来约束时钟的压摆。

7.2.1 时钟不确定度(Clock Uncertainty)

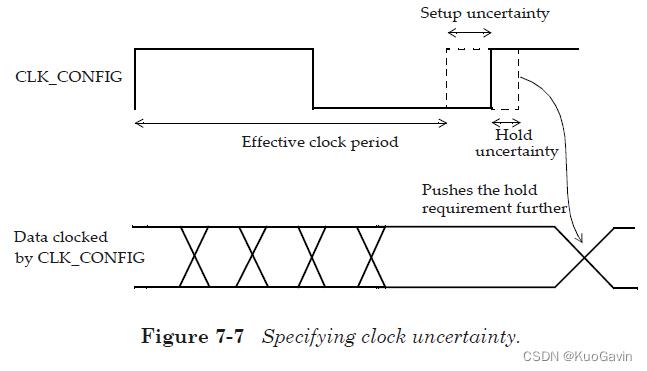

可以使用set_clock_uncertainty约束来指定时钟周期的时序不确定度(uncertainty),该不确定度可用于对可能会减少有效时钟周期的各种因素进行建模。 这些因素可能是时钟抖动(jitter)以及可能需要在时序分析中考虑的任何其它悲观因素。

set_clock_uncertainty -setup 0.2 [get_clocks CLK_CONFIG]

set_clock_uncertainty -hold 0.05 [get_clocks CLK_CONFIG]

注意,建立时间检查的时钟不确定度将减少可用的有效时钟周期,如图7-7所示。对于保持时间检查,时钟不确定度将用作需要满足的额外时序裕量。

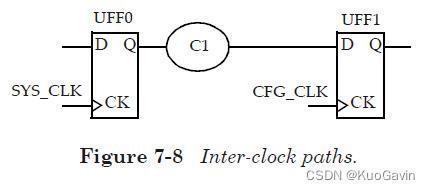

以下命令可用于指定跨时钟边界路径上的时钟不确定度,称为时钟间不确定度(inter-clock uncertainty)。

set_clock_uncertainty -from VIRTUAL_SYS_CLK -to SYS_CLK \\

-hold 0.05

set_clock_uncertainty -from VIRTUAL_SYS_CLK -to SYS_CLK \\

-setup 0.3

set_clock_uncertainty -from SYS_CLK -to CFG_CLK -hold 0.05

set_clock_uncertainty -from SYS_CLK -to CFG_CLK -setup 0.1

图7-8中为两个不同时钟域SYS_CLK和CFG_CLK之间的路径。根据上述时钟间不确定度的约束,将

100

p

s

100ps

100ps用作建立时间检查的不确定度,将

50

p

s

50ps

50ps用作保持时间检查的不确定度。

7.2.2 时钟延迟(Clock Latency)

可以使用set_clock_latency命令指定时钟的延迟。

# Rise clock latency on MAIN_CLK is 1.8ns:

set_clock_latency 1.8 -rise [get_clocks MAIN_CLK]

# Fall clock latency on all clocks is 2.1ns:

set_clock_latency 2.1 -fall [all_clocks]

# The -rise, -fall refer to the edge at the clock pin of a

# flip-flop.

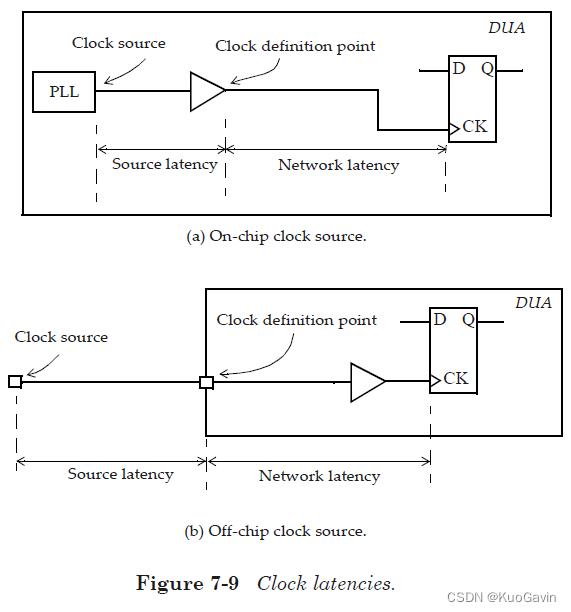

时钟延迟有两种类型:网络延迟(network latency)和源延迟(source latency),触发器时钟引脚上的总时钟延迟是源延迟和网络延迟之和:

- 网络延迟是指从时钟定义点(create_clock)到触发器时钟引脚的延迟;

- 源延迟,也称为插入延迟(insertion delay),是指从时钟源到时钟定义点的延迟,源延迟可能代表片上或片外延迟,图7-9展示了这两种情况;

以下是一些指定源延迟和网络延迟的命令示例:

# Specify a network latency (no -source option) of 0.8ns for

# rise, fall, max and min:

set_clock_latency 0.8 [get_clocks CLK_CONFIG]

# Specify a source latency:

set_clock_latency 1.9 -source [get_clocks SYS_CLK]

# Specify a min source latency:

set_clock_latency 0.851 -source -min [get_clocks CFG_CLK]

# Specify a max source latency:

set_clock_latency 1.322 -source -max [get_clocks CFG_CLK]

源延迟和网络延迟之间的一个重要区别是:一旦为设计建立了时钟树,就可以忽略网络延迟(假设指定了set_propagated_clock命令)。但是,即使在建立时钟树之后,源延迟也会保留。网络延迟是在进行时钟树综合(Clock Tree Synthesis)之前对时钟树延迟的估计值。在时钟树综合完成后,从时钟源到触发器时钟引脚的总时钟延迟是源延迟加上时钟树从时钟定义点到触发器的实际延迟。

下一节将介绍衍生时钟(generated clocks),7.9节将介绍虚拟时钟(virtual clocks)。

7.3 衍生时钟(Generated Clocks)

以上是关于配置STA环境的主要内容,如果未能解决你的问题,请参考以下文章