极智开发 | PaddlePi-K210 硬件架构

Posted 极智视界

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了极智开发 | PaddlePi-K210 硬件架构相关的知识,希望对你有一定的参考价值。

欢迎关注我的公众号 [极智视界],获取我的更多笔记分享

大家好,我是极智视界,本文介绍一下 PaddlePi-K210 硬件架构。

PaddlePi-K210 是为 PaddlePaddle 平台定制开发的终端运算模块,外型紧凑小巧,性能优越,可用于 AI 核心运算处理单元。这里介绍 PaddlePi-K210 硬件架构。

文章目录

1. 片上系统架构

来看 K210 的片上系统架构,上图:

其中各模块的功能如下:

| 功能分类 | 片上系统 | 对应功能 | 是否有引脚 |

|---|---|---|---|

| 运算单元 | FPU | CPU 主控芯片 | x |

| - | KPU | AI加速芯片 | x |

| - | APU | 音频处理器 | x |

| - | FFT | 快速傅里叶变换加速模块 | x |

| 通信接口 | UART | 包含 uart0~3 总共 4 个 uart 接口 | y |

| - | SPI | 0、1、3 为 master,2 为 slave | y |

| - | I2S | 音频数据接入 | y |

| - | I2C | 两线式穿行总线 | y |

| - | JTAG | 嵌入式调试技术 | y |

| 特殊接口 | DVP | 摄像头接口 ( 8 位并口) | y |

| - | FPIOA | 现场可编程 IO 阵列, 用于将芯片内部功能映射到 48 物理 IO | y |

| - | GPIO | 通用 IO | y |

| 功能模块 | RTC | 计时模块 | x |

| - | AES | 高级加密解密加速器 | x |

| - | SHA256 | 哈希计算模块 | x |

| - | Timer | 定时器,可中断 | x |

| - | PWM | PWM 定时器模块,可被 Timer 配置 | x |

| - | WDT | 看门狗定时器 | x |

| - | SRAM | 8M片上内存 | x |

注:以上有部分的带有引脚的模块,其引脚可能是通过 FPIOA 进行配置的,从而进行引出的。

2. 部分接口详解

2.1 UART 通信接口

一种全双工双向传输的通用串行数据总线,用于异步通信。具体有三种通讯协议:RS232、RS485、RS422,不同协议引脚不同。

以下是简化的 通讯模型:

该模型只需要两条通信电路和共地,也就是最少三条线,就可以实现相互的通讯。

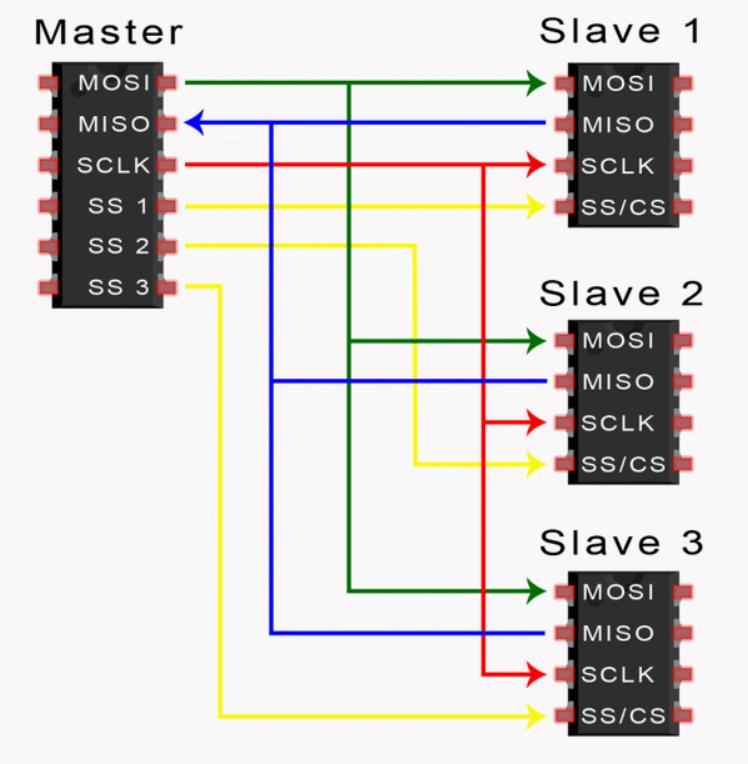

2.2 SPI 通信接口

一种全双工双向传输的通用串行数据总线,同步通信,时钟信号由 Master 生成,也就是主设备。SPI 中只有一个主设备 Master 以及 多个从设备 Slave。

以下是简化的通讯模型:

- MOSI: 信号线,主机输出,从机输入;

- MISO: 信号线,主机输入,从机输出;

- SCLK: 时钟信号线,主机输出,从机输入;

- SS/CS: 片选信号;

当含有多个片选信号的时候,可以采用以下的通讯模型:

当只有一个片选信号的时候,可以采用以下的通讯模型:

2.3 I2C 通信

两线式串行总线,半双工,同步通信。只需要两个总线:一条是双向的串行数据线 SDA,一条是串行时钟线SCL。也是分为了 主机 和 从机 的通信模式。

2.4 JTAG 调试接口

对于 K210,其支持 JTAG 硬件调试功能。而对于 PaddlePi-K210,其配套的 PaddlePi-K210-Debugger 调试器通过一头通过 USB 连接主机,一头使用 JTAG 连接 PaddlePi-K210,实现了 USB2JTAG 的功能,该调试器的具体原理图可见相关资料。另外,在 PaddlePi-K210 中,JTAG 的连接线最终体现在了 BANK0 的 IO_0、IO_1、IO_2、IO_3 这几个接口上。

其具体的接口说明如下:

| 仿真器接口A | 目标板接口B | 信号描述 |

|---|---|---|

| 5V supply | VCC | 电源正极A->B |

| TDI | TDI | 数据输入A->B |

| TMS | TMS | 模式选择A->B |

| TCK | TCK | 时钟信号A->B |

| TDO | TDO | 数据输出A<-B |

| GND | GND | 电源负极A–B |

2.5 USB 接口

PaddlePi-K210 不包含 USB 接口,本意是想要安装一个 TYPE-C 接口,可能需要专门去了解以下 USB 接口的通讯协议。很有可能需要进行通讯协议的转换 USB2UART,使用 CP2102-GMR 转换模块实现。

3 各个模块介绍

3.1 POWER 模块

实现了 5V 的 VIN 电压到 0.9V 和 1.8V 和 3.3V 的电压转换,主要是通过 RY1303 这个 DC-DC 转换器实现。输出的三个不同电压值,后续会接入到 K210 的 POWER 相关引脚上。

实际的原理图如下:

简化的功能图如下:

3.2 TF 卡接口模块

该处改用了 TF卡 的 SPI 操作模式进行接口连接,最终跟 WIFI 的 SPI 接口,分别作为 SPI 的 slave 从机,而 K210 作为 SPI 的 master 主机,同时 master 通过 TF_CS 片选线联通 TF 卡,之后继续相应的通信。

实际的原理图如下:

简化的功能图如下:

3.3 WIFI 模块

W600 是一个 IOT-WIFI 芯片,是一个完整的单片机。这里作为专门的 WIFI 收发处理器,用来实现 WIFI 功能。 作为 SPI 中的 slave 从机跟 K210 进行通信。

实际的原理图如下:

简化的功能图如下:

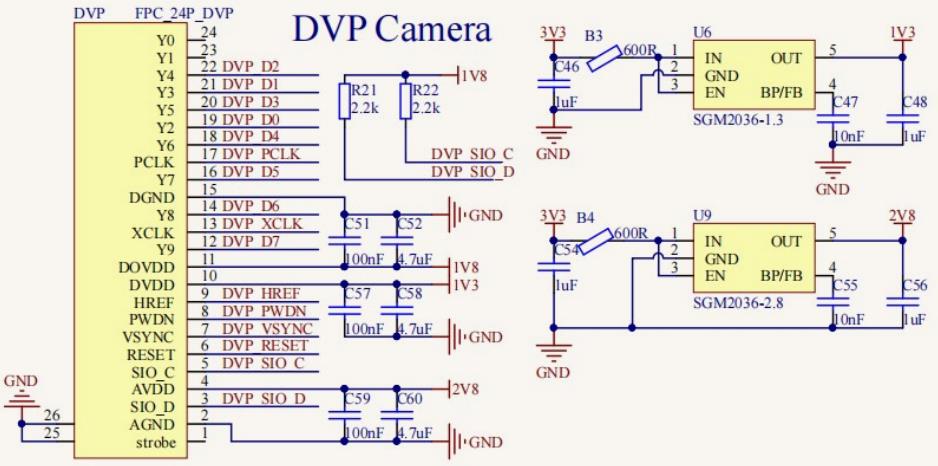

3.4 DVP 相机模块

使用了 DVP 这种传统的 Sensor 传感器接口,用于并行数据传输。实际的原理图如下所示,其中两个SGM2036 是 DC-DC 转换器,用于产生对 DVP 摄像头专门的供电电压:

简化的功能图如下所示:

其中 Sensor 是相机传感器模块,ISP 是 主机模块:

- VSYNC: vertical synchronization,帧同步信号 (DVP_VSYNC);

- HSYNC: horizonal synchronization,行同步信号;

- PCLK: pixel clock ,像素时钟,每个时钟对应一个像素数据 (DVP_PCLK);

- DATA: 像素数据,视频数据,具体位宽要看 ISP 是否支持 (DVP_D0-D7);

- XCLK: 或者 MCLK,ISP 芯片输出给驱动 sensor 的时钟 (DVP_XCLK);

- SCL、SDA: IIC 用来读写 sensor 的寄存器,配置 sensor;

好了,以上分享了 PaddlePi-K210 硬件架构。希望我的分享能对你的学习有一点帮助。

【公众号传送】

搜索关注我的微信公众号【极智视界】,获取我的更多经验分享,让我们用极致+极客的心态来迎接AI !

以上是关于极智开发 | PaddlePi-K210 硬件架构的主要内容,如果未能解决你的问题,请参考以下文章