FPGA+FFT基于FPGA的FFT频率计设计与实现

Posted fpga和matlab

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了FPGA+FFT基于FPGA的FFT频率计设计与实现相关的知识,希望对你有一定的参考价值。

1.软件版本

Quartusii12.1

2.本算法fpga实现过程

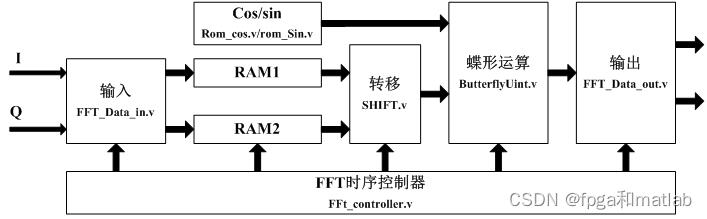

这里,我们的FFT2048模块,其基本结构如下所示:

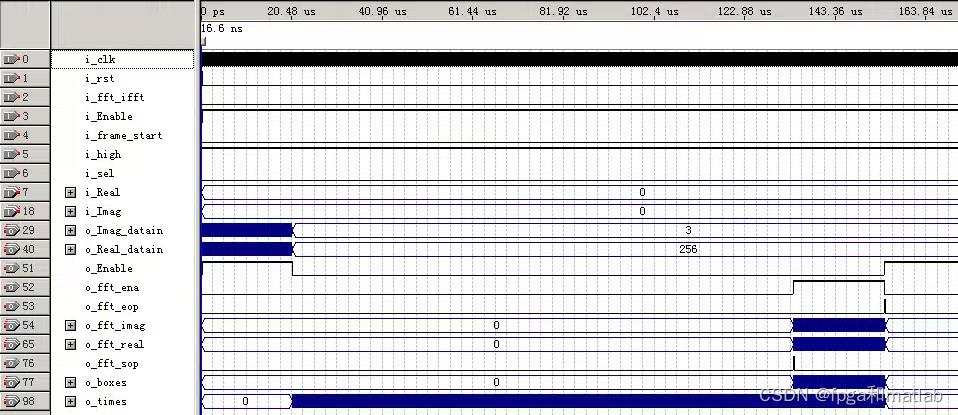

仿真效果如下所示:

| i_rst | 复位信号 | 1的时候复位,0的时候工作 |

| i_clk | 系统时钟 | 时钟,接频率至少为 |

| i_fft_ifft | FFTIFFT | 0的时候为FFT,1的时候为IFFT |

| i_sel | 测试选择 | 0的时候为内部测试,1的时候外部输入测试 |

| i_Imag | 外部测试虚部 | AD输入1 |

| i_Real | 外部测试实部 | AD输入2 |

| o_Real_datain | 测试输出1 | 输入信号的输出 |

| o_Imag_datain | 测试输出2 | 输入信号的输出 |

| i_Enable | 使能 | 即高电平的时候工作 |

| o_Enable | 输出使能 | FFT工作完毕输出数据的时候为1 |

| i_frame_start | 帧头指示 | 在帧头前一时刻输入高电平 |

| o_fft_imag | 虚部 | 输出虚部 |

| o_fft_real | 实部 | 输出实部 |

| i_high | 1 | 一直设置为1即可 |

| o_fft_ena | 输出使能 | 当FFT开始输出结论时,为1,否则为0 |

| o_fft_sop | 输出帧头指示 | |

| o_fft_eop | 输出帧尾指示 | |

| o_times | 统计运行时间 | |

| O_boxes | 实部和虚部的abs模计算 |

前面的几个控制信号,上面介绍过了,下面说明一下如何看这个波形图

当sel选择0的时候,则启用内部的测试信号进行FFT的测试,在实际工作的时候,接的是sel=1,即外部输入信号进行测试。

ireal和iimag就是外部输入信号,因为在仿真阶段,我们使用内部测试结果,所以为0。

最后两个是输出我们使用的测试信号。如果sel=1,则输出外面进来的两路信号,如果sel=0,则输出内部测试的两路信号,这里内部测试的两路信号为cos和sin信号。

Oenable是状态指示信号,0的时候说明FFT正在工作,1的时候计算完毕输出最后的FFT结论

eop和sop分别表示的是最后FFT输出的帧信号的对应的帧尾和帧头

oboxes表示的实部和虚部的平方和,用来看最后的FFT的幅度,也就是matlab中的对FFT最后计算abs模的效果

times是计算运行的时间,具体仿真时间为timesx时钟频率,本课题,我们的计算时间为:+

13380个时钟周期,

那么如果时钟频率为10M

那么延迟为,13380*1/10M = 0.0013s >1ms。

所以,我们在实际使用的时候,只要时钟频率大于10M就可以满足1ms延迟的需求。

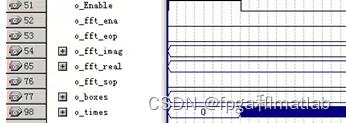

下载板子后使用signalTapII观察效果如下所示:

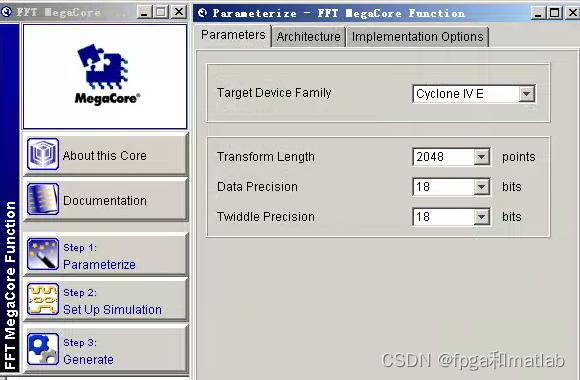

在本系统,FFT采用IP核实现

IP核的设置比较简单,具体如下所示:

设置一:

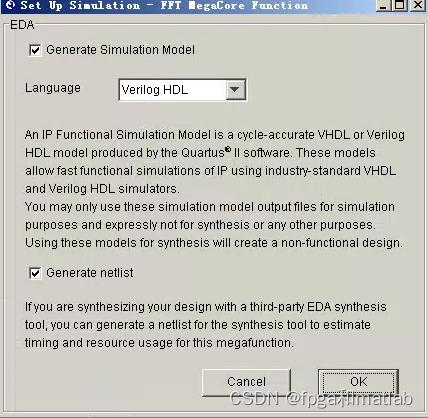

设置二:

上面的产生仿真文件,可以调用内部的模块进行仿真。

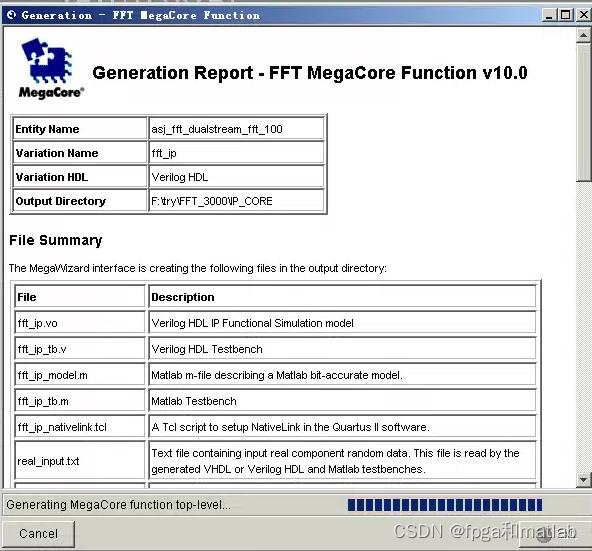

最后完成设置:

其实是用IP核掌握好几个接口的信号的输入定义,就基本可以快速使用了,下面介绍一个FFT核各个管脚的使用.

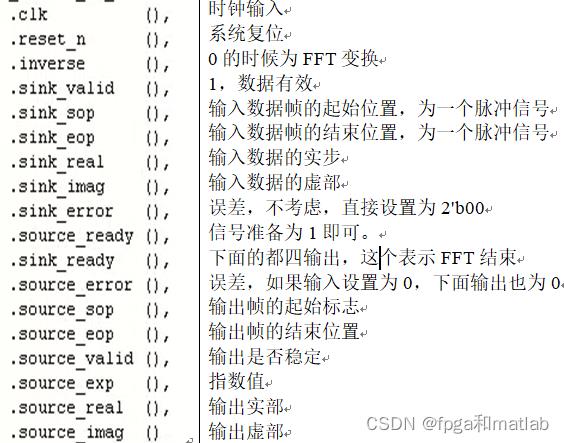

下面重点介绍一下IP核设置后的FFT核的各个接口的含义:

关于IP核的详细介绍就不做说明了,比较简单。IP核仿真如下所示:

3.部分源码

module fft_tops(

i_clk,

i_rst,

i_sop,

i_eop,

i_datar,

i_datai,

o_datar,

o_datai

);

input i_clk;

input i_rst;

input i_sop;

input i_eop;

input [17:0]i_datar;

input [17:0]i_datai;

output[17:0]o_datar;

output[17:0]o_datai;

fft_ip fft_ip_u(

.clk (i_clk),

.reset_n (i_rst),

.inverse (1'b0),

.sink_valid (1'b1),

.sink_sop (i_sop),

.sink_eop (i_eop),

.sink_real (i_datar),

.sink_imag (i_datai),

.sink_error (2'b00),

.source_ready (1'b1),

.sink_ready (),

.source_error (),

.source_sop (),

.source_eop (),

.source_valid (),

.source_exp (),

.source_real (o_datar),

.source_imag (o_datai)

);

endmodule

A28-15以上是关于FPGA+FFT基于FPGA的FFT频率计设计与实现的主要内容,如果未能解决你的问题,请参考以下文章