Rockchip RK3588 MIPI-DSI2 详解

Posted Walnut-Huang

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了Rockchip RK3588 MIPI-DSI2 详解相关的知识,希望对你有一定的参考价值。

Rockchip RK3588 MIPI-DSI2 详解

目录

文章目录

- Rockchip RK3588 MIPI-DSI2 详解

- @[toc]

- Introduction

- MIPI-DSI2 Features

- MIPI DSI-2 Host 与 MIPI DSI Host 的差别

- MIPI DPHY 差别

- 应用领域

- 驱动代码说明:

-

- 屏端配置

-

- Display Route

-

- 开机LOGO

-

- DSI HOST

-

- DCPHY

-

- 协议分析

-

- 常见问题

-

- @[toc]

- Introduction

- MIPI-DSI2 Features

- MIPI DSI-2 Host 与 MIPI DSI Host 的差别

- MIPI DPHY 差别

- 应用领域

- 驱动代码说明:

- 屏端配置

- Display Route

- 开机LOGO

- DSI HOST

- DCPHY

- 协议分析

- 常见问题

Introduction

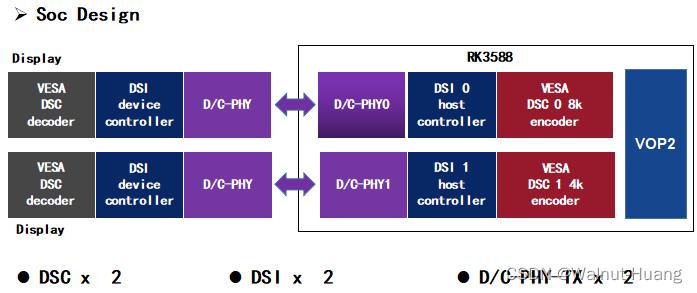

DSI-2 是 MIPI 联盟定义的一组通信协议的一部分, DWC-MIPI-DSI2 是一个实现 MIPI-DSI2 规范中定义的所有协议功能的数字核控制器,可以兼容 D-PHY 和 C-PHY 的物理接口,支持两路的 Display Stream Compression (DSC) 数据传输, RK3588 有两个 DSI-2 控制器和两个独立的物理的 D/C-PHY, 可以同时最多支持两路 MIPI 输出。

MIPI-DSI2 Features

- MIPI® Alliance Specification for Display Serial Interface 2 (DSI-2) Version 1.1

- MIPI® Alliance Specification for Display Command Set (DCS) Version 1.4

- MIPI® Alliance Specification for D-PHY v2.0

- MIPI® Alliance Specification for C-PHY v1.1

- Four data lanes on D-PHY and three data trios on C-PHY

- Bidirectional communication and escape mode through data lane 0

- Continuous and non-continuous clock modes on D-PHY and non-continuous clock mode on C-PHY

- End of Transmission packet (EoTp)

- Scrambling

- VESA DSC 1.1/1.2a

- Up to 4.5 Gbps per lane in D-PHY

- Up to 2.0 Gsps per trio in C-PHY

MIPI DSI-2 Host 与 MIPI DSI Host 的差别

MIPI DSI-2 除了可以兼容 MIPI DSI 的所有协议功能外, 还增加支持 MIPI C-PHY.

MIPI DPHY 差别

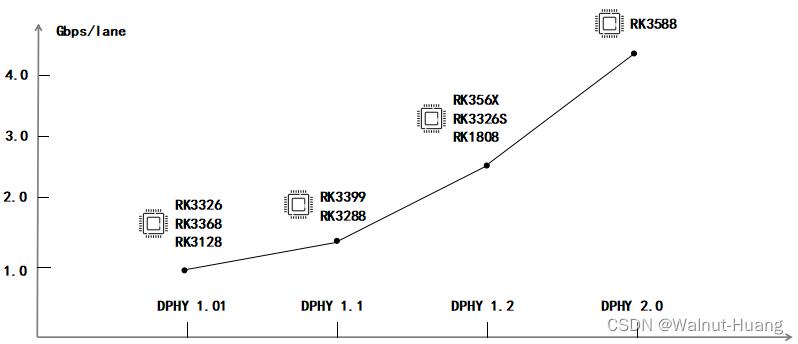

RK3588 平台 MIPI DPHY 不同以往平台 MIPI DPHY 版本, 其带宽最高可以到 4.5 Gbps.

应用领域

MIPI DSI基于差分信号传输,可以降低引脚数量和硬件设计复杂度,并保持良好的硬件兼容性。另外,基于MIPI DSI协议的IP还具备低功耗、低EMI的特性。

其应用领域如下图:

驱动代码说明:

uboot

驱动位置

drivers/video/drm/dw_mipi_dsi2.c

drivers/video/drm/samsung_mipi_dcphy.c

驱动配置

CONFIG_DRM_ROCKCHIP_DW_MIPI_DSI2=y

CONFIG_DRM_ROCKCHIP_SAMSUNG_MIPI_DCPHY=y

kernel

驱动位置

MIPI DSI-2 host controller:

drivers/gpu/drm/rockchip/dw-mipi-dsi2-rockchip.c

MIPI DCPHY:

drivers/phy/rockchip/phy-rockchip-samsung-dcphy.c

驱动配置

cONFIG_ROCKCHIP_DW_MIPI_DSI=y

CONFIG_PHY_ROCKCHIP_SAMSUNG_DCPHY=y

参考设备树

DTS 路径:

arch/arm64/boot/dts/rockchip/rk3588-evb.dtsi

arch/arm64/boot/dts/rockchip/rk3588-evb1-lp4.dtsi

arch/arm64/boot/dts/rockchip/rk3588-evb2-lp4.dtsi

arch/arm64/boot/dts/rockchip/rk3588-evb3-lp5.dtsi

arch/arm64/boot/dts/rockchip/rk3588-evb4-lp4.dtsi

arch/arm64/boot/dts/rockchip/rk3588s-evb.dtsi

arch/arm64/boot/dts/rockchip/rk3588s-evb1-lp4x.dtsi

arch/arm64/boot/dts/rockchip/rk3588s-evb2-lp5.dtsi

arch/arm64/boot/dts/rockchip/rk3588s-evb4-lp4x.dtsi

dts 配置用例场景说明:

rk3588-evb1: dsi0->dphy->1080p_panel && dsi1->dphy->1080p_panel;

rk3588-evb2: dsi1->dphy->1080p_panel;

rk3588-evb3: dsi0->dphy->1080p_panel && dsi1->cphy->cphy_panel;

rk3588-evb4: dsi0->dphy->1080p_panel;

rk3588s-evb1: dsi0->dphy->1080p_panel && dsi1->dphy->cmd_no_dsc_panel;

rk3588s-evb2: dsi0->cphy->cphy_panel & dsi1->dphy->1080p_panel;

rk3588s-evb4: dsi0->dphy->1080p_panel && dsi1->dphy->cmd_dsc_panel;

屏端配置

DTS 配置

dsi0_panel: panel@0

status = "okay";

compatible = "simple-panel-dsi";

reg = <0>;

power-supply = <&vcc3v3_lcd_n>;

backlight = <&backlight>;

reset-gpios = <&gpio2 RK_PB4 GPIO_ACTIVE_LOW>;

reset-delay-ms = <10>;

enable-delay-ms = <10>;

prepare-delay-ms = <10>;

unprepare-delay-ms = <10>;

disable-delay-ms = <60>;

dsi,flags = <(MIPI_DSI_MODE_VIDEO | MIPI_DSI_MODE_VIDEO_BURST |

MIPI_DSI_MODE_LPM | MIPI_DSI_MODE_EOT_PACKET)>;

dsi,format = <MIPI_DSI_FMT_RGB888>;

dsi,lanes = <4>;

//phy-c-option;

//compressed-data;

//slice-width = <720>;

//slice-height = <65>;

//version-major = <1>;

//version-minor = <1>;

panel-init-sequence = [

...

05 78 01 11

05 00 01 29

];

panel-exit-sequence = [

05 00 01 28

05 00 01 10

];

disp_timings0: display-timings

native-mode = <&dsi0_timing0>;

dsi0_timing0: timing0

clock-frequency = <132000000>;

hactive = <1080>;

vactive = <1920>;

hfront-porch = <15>;

hsync-len = <4>;

hback-porch = <30>;

vfront-porch = <15>;

vsync-len = <2>;

vback-porch = <15>;

hsync-active = <0>;

vsync-active = <0>;

de-active = <0>;

pixelclk-active = <0>;

;

;

;

配置说明

通用配置

| Property | Description | Value |

|---|---|---|

| compatible | compatible | simple-panel-dsi |

| power-supply | 屏端供电 [option] | 相关regulator引用 |

| backlight | 背光 | 背光引用 |

| enable-gpios | 屏使能GPIO [option] | GPIO引用描述 |

| reset-gpios | 屏复位GPIO | GPIO引用描述 |

| reset-delay-ms | panel sequence delay | 参考 panel spec |

| enable-delay-ms | ||

| prepare-delay-ms | ||

| unprepare-delay-ms | ||

| disable-delay-ms | ||

| dsi,flags | DSI2 工作模式 | cmd mode: MIPI_DSI_MODE_LPM | MIPI_DSI_MODE_EOT_PACKET |

| video mode: MIPI_DSI_MODE_VIDEO | MIPI_DSI_MODE_VIDEO_BURST | MIPI_DSI_MODE_LPM | MIPI_DSI_MODE_EOT_PACKET | ||

| dsi,format | 像素数据格式 | MIPI_DSI_FMT_RGB888 |

| MIPI_DSI_FMT_RGB666 | ||

| MIPI_DSI_FMT_RGB666_PACKED | ||

| MIPI_DSI_FMT_RGB565 | ||

| dsi,lanes | mipi data 通道数 | 1/2/3 trios [cphy] |

| 6 trios [cphy 双通道] | ||

| 1/2/3/4 lanes [dphy] | ||

| 8 lanes [dphy 双通道] | ||

| phy-c-option | C-PHY panel [option] | 布尔类型string |

| compressed-data | 带DSC panel [option] | 布尔类型string |

| slice-width | 定义dsc slice宽 [option] | 参照panel spec |

| slice-height | 定义dsc slice高 [option] | |

| version-major | 定义dsc版本 [option] | 参照panel spec |

| version-minor | ||

| panel-init-sequence | 屏上电初始化序列 | [hex] data_type delay_ms payload_lenth payload |

| panel-exit-sequence | 屏下电初始化序列 | |

| display-timing | panel timing | 参考panel spec |

display Timing

[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-UOZ8oGbq-1657674965348)(Rockchip_RK3588_Developer_Guide_MIPI_DSI2/Display-Timing.png)]

dsi,flags

CLK Type

默认情况, MIPI DPHY 的时钟通道是连续模式,如下图:

当 MIPI_DSI_CLOCK_NON_CONTINUOUS 追加到 dsi,flags 时,MIPI DPHY 的时钟通道将会配置成非连续模式,如下图:

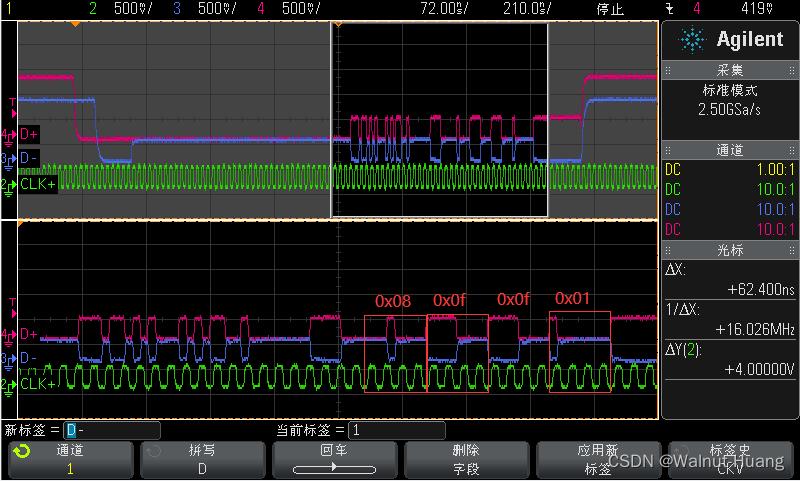

Eotp

Eotp 是一个短包用于指示数据链路上高速传输的结束。Eotp 主要作用是增强系统高速传输通信的稳健性,出于这个目的,DSI 不需要在 LP 模式发送 Eotp。

Eotp 不同于其他 DSI 包,它有固定的格式:

Data Type = DI [5:0] = 0b001000

Virtual Channel = DI [7:6] = 0b00

Payload Data [15:0] = 0x0F0F

ECC [7:0] = 0x01

将 MIPI_DSI_MODE_EOT_PACKET 追加到 dsi,flags 属性可以开关 Soc MIPI DSI TX 在高速模式发送 Eotp。

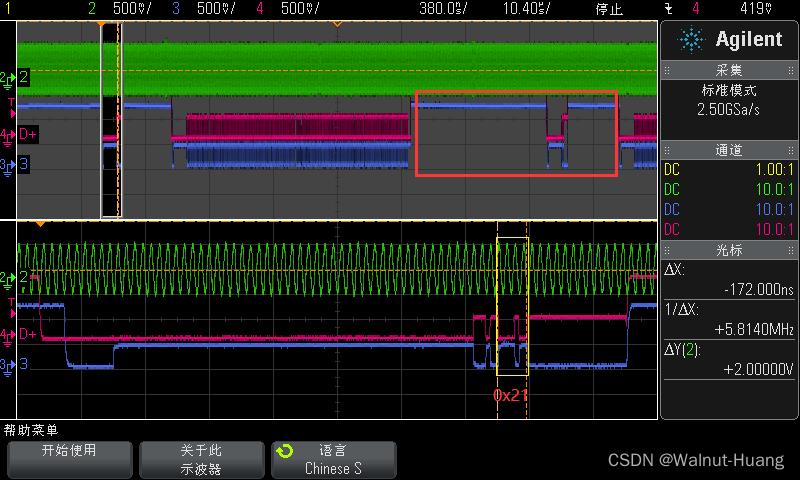

如下是在 HSDT 模式下捕获 Eotp 波形:

BLANK_HS_EN

在数据通道,一般存在一行会有两个 LP11 消隐, 如下图:

但往往有些显示模组或者外接 MIPI 转接芯片,不支持在 Hblank阶段有两个 LP-11, 可以将 BLK_HFP_HS_EN 或 BLK_HBP_HS_EN 追加到 dsi,flags 属性,使HFP 或 HBP 以高速的形式存在。

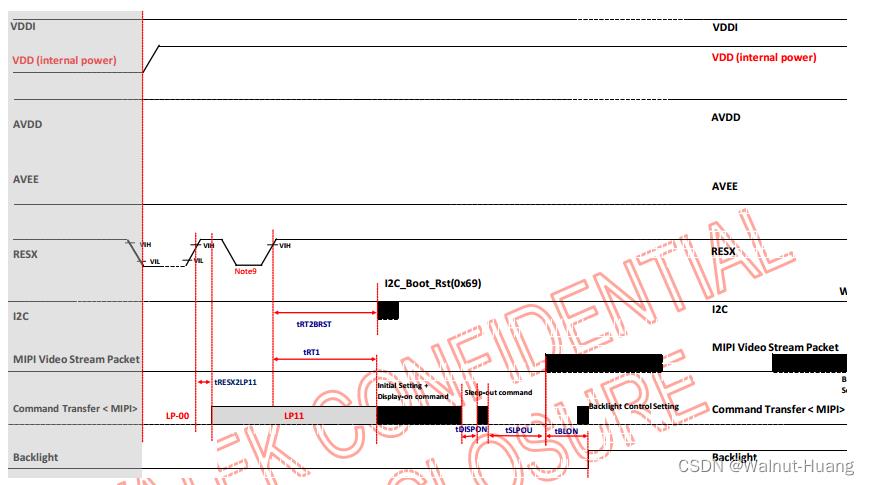

屏上电时序

屏下电时序

初始化序列常见数据类型

| data type | description | packet size |

|---|---|---|

| 0x03 | Generic Short WRITE, no parameters | short |

| 0x13 | Generic Short WRITE, 1 parameters | short |

| 0x23 | Generic Short WRITE, 2 parameters | short |

| 0x29 | Generic long WRITE, | long |

| 0x05 | DCS Short WRITE, no parameters | short |

| 0x15 | DCS Short WRITE, 1 parameters | short |

| 0x07 | DCS Short WRITE, 1 parameters, DSC EN | short |

| 0x0a | DCS long WRITE, PPS, 128 bytes | long |

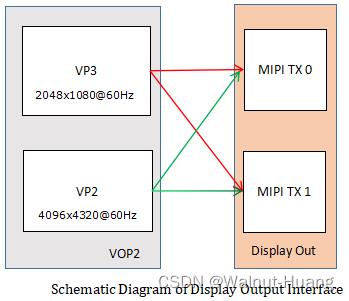

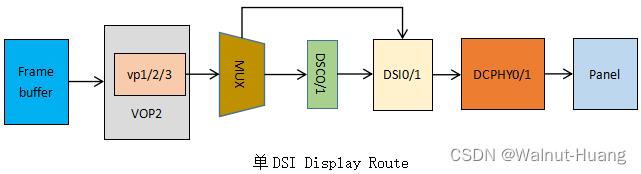

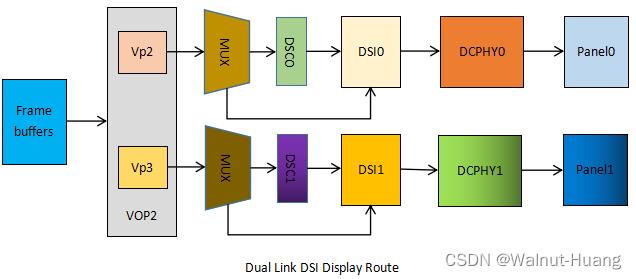

Display Route

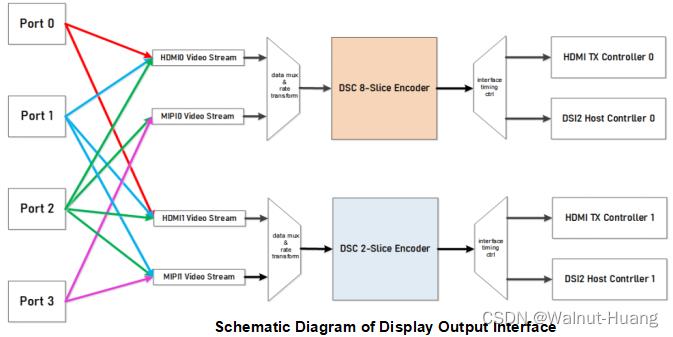

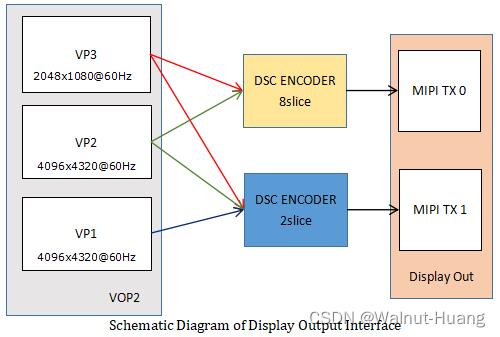

MIPI with DSC

MIPI with DSC Bypass

DTS 配置

如 DSI0 挂载在 VP3:

&dsi0_in_vp2

status = "disabled";

;

&dsi0_in_vp3

status = "okay";

;

如 DSI1 挂载 VP2:

&dsi1_in_vp2

status = "okay";

;

&dsi1_in_vp3

status = "disabled";

;

开机LOGO

route_dsi0

例如 vp3->dsi0 或 vp3->dsc0->dsi0:

&route_dsi0

status = "okay";

connect = <&vp3_out_dsi0>;

;

route_dsi1

例如 vp2->dsi1 或 vp2->dsc1->dsi1:

&route_dsi1

status = "okay";

connect = <&vp2_out_dsi1>;

;

route_dsi0 && route_dsi1

例如 (vp3->dsi0 或 vp3->dsc0->dsi0) && (vp2->dsi1 或 vp2->dsc1->dsi1):

&route_dsi0

status = "okay";

connect = <&vp3_out_dsi0>;

;

&route_dsi1

status = "okay";

connect = <&vp2_out_dsi1>;

;

DSI HOST

ports

以下实例中 ports 是用来 Dispaly Interface 和 panel 之间进行关联。

详细配置说明参阅如下文档:

Documentation/devicetree/bindings/graph.txt

单 DSI

DSI0

&dsi0

status = "okay";

//rockchip,lane-rate = <1000>;

dsi0_panel: panel@0

status = "okay";

compatible = "simple-panel-dsi";

...

ports

#address-cells = <1>;

#size-cells = <0>;

port@0

reg = <0>;

panel_in_dsi: endpoint

remote-endpoint = <&dsi_out_panel>;

;

;

;

;

ports

#address-cells = <1>;

#size-cells = <0>;

port@1

reg = <1>;

dsi_out_panel: endpoint

remote-endpoint = <&panel_in_dsi>;

;

;

;

;

&mipi_dcphy0

status = "okay";

;

DSI1

&dsi1

status = "okay";

//rockchip,lane-rate = <1000>;

dsi1_panel: panel@0

status = "okay";

compatible = "simple-panel-dsi";

...

ports

#address-cells = <1>;

#size-cells = <0>;

port@0

reg = <0>;

panel_in_dsi1: endpoint

remote-endpoint = <&dsi1_out_panel>;

;

;

;

;

ports

#address-cells = <1>;

#size-cells = <0>;

port@1

reg = <1>;

dsi1_out_panel: endpoint

remote-endpoint = <&panel_in_dsi1>;

;

;

;

;

&mipi_dcphy1

status = "okay";

;

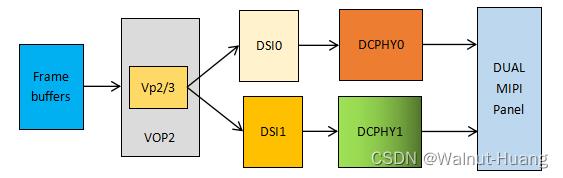

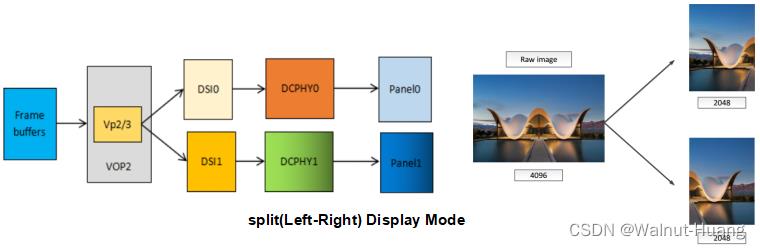

双通道 DSI

MODE1:

MODE2:

双通道的配置注意如下标红属性:

rockchip,dual-channel = <&dsi1>

dsi,lanes = <8>;//DPHY 屏, CPHY 屏值改成 6

&dsi0

status = "okay";

rockchip,dual-channel = <&dsi1>;

dsi0_panel

status = "okay";

compatible = "simple-panel-dsi";

dsi,lanes = <8>;

...

display-timings

native-mode = <&timing0>;

timing0: timing0

clock-frequency = <260000000>;

hactive = <1440>;

vactive = <2560>;

hfront-porch = <150>;

hsync-len = <30>;

hback-porch = <60>;

vfront-porch = <8>;

vsync-len = <4>;

vback-porch = <4>;

hsync-active = <0>;

vsync-active = <0>;

de-active = <0>;

pixelclk-active = <0>;

;

;

ports

#address-cells = <1>;

#size-cells = <0>;

port@0

reg = <0>;

panel_in_dsi0: endpoint

remote-endpoint = <&dsi0_out_panel>;

;

;

;

;

ports

#address-cells = <1>;

#size-cells = <0>;

port@1

reg = <1>;

dsi0_out_panel: endpoint

remote-endpoint = <&panel_in_dsi0>;

;

;

;

;

&dsi1

status = "okay";

;

&mipi_dcphy0

status = "okay";

;

&mipi_dcphy1

status = "okay";

;

Dual-link DSI

&dsi0

status = "okay";

//rockchip,lane-rate = <1000>;

dsi0_panel: panel@0

status = "okay";

compatible = "simple-panel-dsi";

...

ports

#address-cells = <1>;

#size-cells = <0>;

port@0

reg = <0>;

panel_in_dsi: endpoint

remote-endpoint = <&dsi_out_panel>;

;

;

;

;

ports

#address-cells = <1>;

#size-cells = <0>;

port@1

reg = <1>;

dsi_out_panel: endpoint

remote-endpoint = <&panel_in_dsi>;

;

;

;

;

&dsi1 status = "okay";

//rockchip,lane-rate = <1000>;

dsi1_panel: panel@0

status = "okay";

compatible = "simple-panel-dsi";

...

ports

#address-cells = <1>;

#size-cells = <0>;

port@0

reg = <0>;

panel_in_dsi1: endpoint

remote-endpoint = <&dsi1_out_panel>;

;

;

;

;

ports

#address-cells = <1>;

#size-cells = <0>;

port@1

reg = <1>;

dsi1_out_panel: endpoint

remote-endpoint = <&panel_in_dsi1>;

;

;

;

;

&mipi_dcphy0

status = "okay";

;

&mipi_dcphy1

status = "okay";

;

DCPHY

实际应用配置中默认是配置成D-PHY,通过屏端配置介绍可知,通过下面可以配置成 C-PHY:

dsi0_panel: panel@0

...

phy-c-option;

...

;

D-PHY

1. Up to 4.5 Gbps per lane in D-PHY

2. 一个D-PHY port 最多4lanes,每个lane由两条差分线组成

C-PHY

1. Up to 2.0 Gsps per trio in C-PHY

2. 一个C-PHY port 最多3lanes,每个lane由 tree-wire-trios 组成

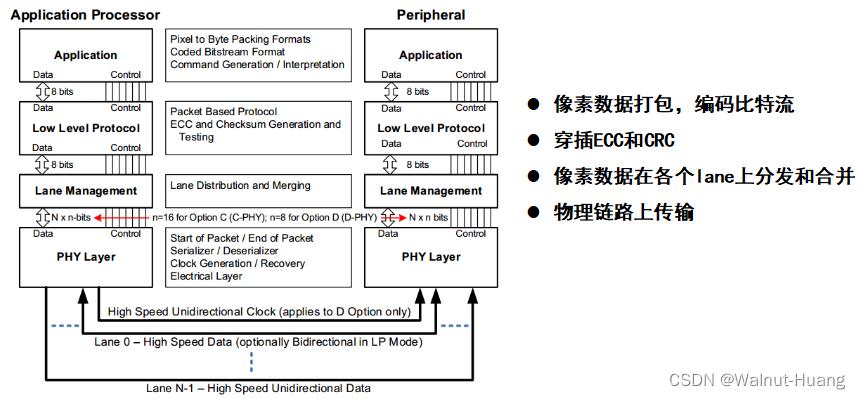

协议分析

DSI Layer Definitions

D Option

Lane states and line levels

固件有两种格式:

-

原始固件(raw firmware)

-

RK固件(Rockchip firmware)

原始固件,是一种能以逐位复制的方式烧写到存储设备的固件,是存储设备的原始映像。原始固件一般烧写到 SD 卡中,但也可以烧写到 eMMC 中。 烧写原始固件有许多工具可以选用:

-

烧写 SD 卡

-

图形界面烧写工具:

-

SDCard Installer (Linux/Windows/Mac)

-

Etcher (Linux/Windows/Mac)

-

-

命令行烧写工具

-

dd (Linux)

-

-

-

烧写 eMMC

-

图形界面烧写工具:

-

AndroidTool (Windows)

-

-

命令行烧写工具:

-

upgrade_tool (Linux)

-

rkdeveloptool (Linux)

-

-

RK 固件,是以 Rockchip专有格式打包的固件,使用 Rockchip 提供的工具可以烧写到 eMMC 或者 SD 卡中。 烧写RK 固件有以下工具可以选用:

-

烧写 SD 卡

-

图形界面烧写工具:

-

SD Firmware Tool (Windows)

-

-

-

烧写 eMMC

-

图形界面烧写工具:

-

AndroidTool (Windows)

-

-

命令行烧写工具:

-

upgrade_tool (Linux)

-

-

分区映像,是分区的映像数据,用于存储设备对应分区的烧写。例如,编译 Android SDK会构建出 boot.img、kernel.img和system.img等分区映像文件,kernel.img 会被写到eMMC 或 SD 卡的 “kernel” 分区。