74hc595存储寄存器引脚是否可以悬空?他的原理是否让数据暂停?

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了74hc595存储寄存器引脚是否可以悬空?他的原理是否让数据暂停?相关的知识,希望对你有一定的参考价值。

74HC595 的工作原理 74HC595 的工作原理-编程-显示 SCH 74HC595 是具有 8 位移位寄存器和一个存储器,三态输出功能。 移位寄存器和存 储器是分别的时钟。 数据在 11 SHcp(SCLK P0.4)的上升沿输入,在 12 STcp(nCS P0.8)的上升 P0.4) P0.8) ( ( 沿进入的存储寄存器中去。如果两个时钟连在一起,则移位寄存器总是比存储寄存器早一个 脉冲。 移位寄存器有一个串行移位输入 14 (Ds) P0.6) 和一个串行输出 9 (Q7’) MISO (MOSI P0.6), ( P0.5) P0.5),和一个异步的低电平复位,存储寄存器有一个并行 8 位的,具备三态的总线输出,当 使能 OE 时(为低电平),存储寄存器的数据输出到总线。 74HC595 各个引脚的功能: Q1~7 是并行数据输出口,即储寄存器的数据输出口 Q7' 串行输出口,其应该接 SPI 总线的 MISO 接口 STcp 存储寄存器的时钟脉冲输入口 SHcp 移位寄存器的时钟脉冲输入口 OE 的非 输出使能端 MR 的非 芯片复位端 Ds 串行数据输入端 程序说明: 每当 SHcp(SCLK)(SCLK P0.4)上升沿到来时,DS(MOSI P0.6) P0.4) ( (MOSI P0.6)引脚当前电平值 在移位寄存器中左移一位,在下一个上升沿到来时移位寄存器中的所有位都会向左移一位, 同时 Q7'( MISO) ( MISO P0.5) P0.5)也会串行输出移位寄存器中高位的值,这样连续进行 8 次,就 可以把数组中每一个数(8 位的数)送到移位寄存器;然后当 STcp(nCS)(nCS P0.8)上升 P0.8) ( 沿到来时,移位寄存器的值将会被锁存到锁存器里,并从 Q1~7 引脚输出。 //74HC595 串行输出数据 void outdisp(unsigned char num) unsigned char i; for (i=0;i<8;i++ ) DS=num; SHCP=1; SHCP=0; num<<=1; 设计显示 PCB 板(595 一为传送位选信号,一为传送代码段信号) CEPARK AVR 单片机 之 HC595 驱动数码管显示 (2009-09-16 17:30:13) 标签: 分类:Avr it 这里我用的 CEPARK 的 M64 AVR 开发板,这一课的重点是学会如何使用 74HC595 来驱动数码管。 74HC595 是具有 8 位移位寄存器和一个存储器,三态输出功能。移位寄存器和存储器是分别的时 钟。数据在 SHcp 的上升沿输入,在 STcp 的上升沿进入的存储寄存器中去。如果两个时钟连在一起,则移 位寄存器总是比存储寄存器早一个脉冲。移位寄存器有一个串行移位输入(Ds),和一个串行输出(Q7’), 和一个异步的低电平复位,存储寄存器有一个并行 8 位的,具备三态的总线输出,当使能 OE 时(为低电 平),存储寄存器的数据输出到总线。 引脚说明: QA--QH: 八位并行输出端,可以直接控制数码管的 8 个段。 QH': 级联输出端。我将它接下一个 595 的 SI 端。 SER(DS): 串行数据输入端。 74595 的控制端说明: /SCLR(MR)(10 脚): 低点平时将移位寄存器的数据清零。通常我将它接 Vcc。 SCK(SHCP)(11 脚):上升沿时数据寄存器的数据移位。QA-->QB-->QC-->...-->QH;下降沿移位寄存器数据 不变。(脉冲宽度:5V 时,大于几十纳秒就行了。我通常都选微秒级) RCK(STCP)(12 脚):上升沿时移位寄存器的数据进入数据存储寄存器,下降沿时存储寄存器数据不变。通 常我将 RCK 置为低电平,当移位结束后,在 RCK 端产生一个正脉冲(5V 时,大于几十纳秒就行了。我通常 都选微秒级),更新显示数据。 /G(OE)(13 脚): 高电平时禁止输出(高阻态)。如果单片机的引脚不紧张,用一个引脚控制它,可以方便 地产生闪烁和熄灭效果。比通过数据端移位控制要省时省力。 注:74164 和 74595 功能相仿,都是 8 位串行输入转并行输出移位寄存器。74164 的驱动电流(25mA)比 74595(35mA)的要小,14 脚封装,体积也小一些。 74595 的主要优点是具有数据存储寄存器,在移位的过程中,输出端的数据可以保持不变。这在串行速度 慢的场合很有用处,数码管没有闪烁感。 与 164 只有数据清零端相比,595 还多有输出端时能/禁止控制端,可以使输出为高阻态。 注明:74HC595 引脚命名我现在看到两种,如串行数据输入端(14 脚)有的 Datasheet 上叫 SER,还有一种 叫 DS。不过这都没有关系,只是名字不一样,大家看这些文档时,注意点就行。 现在大家对 595 有了一定的了解,现在我们看 CEPARK AVR 单片机开发板上这一部分的原理图: 大家这里只要注意 11,12,14 这三个引脚由单片机的哪几个口控制就好。 SHCP(11)-----------PG0 STCP(12)-----------PG1 DS(14)-------------PG2 下面是源程序: 效果:第一位和第二位数码管显示 5; #include <avr/io.h> #include <util/delay.h> #define SER_PORT PORTG //PG 口 #define SER_DATA PG2 //DS,串行数据入口 #define SER_RCK PG1 //STCP,来一个上升沿时数据进入并行输出 #define SER_SCK PG0 //SHCP,来一个上升沿时数据移位 unsigned char Led_Disbuf[10]=0xC0,0xF9,0xA4,0xB0,0x99,0x92,0x82,0xF8,0x80,0x90; //共阳极 void Send_Byte_HC595(unsigned char byte) //并行数据移位输出函数 一个数码管亮 //byte 是表示我们想哪一位数码管亮, 如为 0x01,表示第 unsigned char i; //循环变量 for(i = 0;i < 8;i++) if(byte & 0x80) SER_PORT |= _BV(SER_DATA); //PG2 输出 1 else SER_PORT &= ~_BV(SER_DATA);//PG2 输出 0 SER_PORT |= _BV(SER_SCK); //上升沿触发,SER_DATA 数据进入移位寄存器 _delay_us(5); SER_PORT &= ~_BV(SER_SCK); byte <<= 1; //通过左移,逐个点亮个个数码管 SER_PORT |= _BV(SER_RCK); //上升沿触发,移位寄存器中的数据并行输出 _delay_us(5); SER_PORT &= ~_BV(SER_RCK); int main(void) PORTB = 0xff; //PB 口赋初值为 ff DDRB = 0xff; //PB 口为输出态 PORTG = 0x00; //PG 口赋初值为 0 DDRG |= _BV(SER_DATA)|_BV(SER_RCK)|_BV(SER_SCK); //PG0,PG1,PG2 为输出态 PORTB = Led_Disbuf[5]; //数码管上显示 5 Send_Byte_HC595(0x03); //第一位,第二位数码管点亮 while(1) ; 参考技术A 74HC595是硅结构的CMOS器件, 兼容低电压TTL电路,遵守JEDEC标准。 74HC595是具有8位移位寄存器和一个存储器,三态输出功能。 移位寄存器和存储器是分别的时钟。 数据在SHcp的上升沿输入,在STcp的上升沿进入到存储寄存器中去。如果两个时钟连在一起,则移位寄存器总是比存储寄存器早一个脉冲。 移位寄存器有一个串行移位输入(Ds),和一个串行输出(Q7’),和一个异步的低电平复位,存储寄存器有一个并行8位的,具备三态的总线输出,当使能OE时(为低电平),存储寄存器的数据输出到总线。 8位串行输入/输出或者并行输出移位寄存器,具有高阻关断状态。三态。 编辑本段特点 8位串行输入 /8位串行或并行输出 存储状态寄存器,三种状态 输出寄存器可以直接清除 100MHz的移位频率 编辑本段输出能力 并行输出,总线驱动; 串行输出;标准中等规模集成电路 595移位寄存器有一个串行移位输入(Ds),和一个串行输出(Q7’),和一个异步的低电平复位,存储寄存器有一个并行8位的,具备三态的总线输出,当使能OE时(为低电平),存储寄存器的数据输出到总线。 参考数据 Cpd决定动态的能耗, Pd=Cpd×VCC×f1+∑(CL×VCC^2×f0) F1=输入频率,CL=输出电容 f0=输出频率(MHz) Vcc=电源电压 编辑本段引脚说明 符号 引脚 描述 Q0…Q7 第15脚, 1, 7 并行数据输出 GND 第8脚 地 Q7’ 第9脚 串行数据输出 MR 第10脚 主复位(低电平) SHCP 第11脚 移位寄存器时钟输入 STCP 第12脚 存储寄存器时钟输入 OE 第13脚 输出有效(低电平) DS 第14脚 串行数据输入 VCC 第16脚 电源 编辑本段功能表 输入 输出 功能 SHCP STCP OE MR DS Q7’ Qn × × L ↓ × L NC MR为低电平时仅仅影响移位寄存器 × ↑ L L × L L 空移位寄存器到输出寄存器 × × H L × L Z 清空移位寄存器,并行输出为高阻状态 ↑ × L H H Q6 NC 逻辑高电平移入移位寄存器状态0,包含所有的移位寄存器状态 移入,例如,以前的状态6(内部Q6”)出现在串行输出位。 × ↑ L H × NC Qn’ 移位寄存器的内容到达保持寄存器并从并口输出 ↑ ↑ L H × Q6’ Qn’ 移位寄存器内容移入,先前的移位寄存器的内容到达保持寄存器并出。 编辑本段注释 H=高电平状态 L=低电平状态 ↑=上升沿 ↓=下降沿 Z=高阻 NC=无变化 ×=无效 当MR为高电平,OE为低电平时,数据在SHCP上升沿进入移位寄存器,在STCP上升沿输出到并行端口。 编辑本段程序样例 void HC595_senddata(unsigned char dat) unsigned char i; for(i=0;i<8;i++) //发送一个八位数据 if((dat=dat<<i)&0x80==0)MOSIO=0; //第i位为0时,MOSIO发送0; else MOSIO=1; //否则发送1; SH_CLK=0; //SH_CLK的上升沿,将数据送进移位寄存器; NOP(); NOP(); SH_CLK=1; ST_CLK=0; //ST_CLK的上升沿,将数据由移位寄存器送到存储寄存器 NOP(); //并输出到Q0—Q7并口 NOP(); ST_CLK=1; 大致上就是这样子,把MOSIO输入的串行数据,转换到Q0—Q7的并行输出,我用的595芯片,输出是反向的,即是输入1时,输出为0 参考技术B 74HC595是具有8位移位寄存器和一个存储器,三态输出功能。 移位寄存器和存储器是分别的时钟。数据在SCHcp的上升沿输入,在STcp的上升沿进入的存储寄存器中去。如果两个时钟连在一起,则移位寄存器总是比存储寄存器早一个脉冲。移位寄存器有一个串行移位输入(Ds),和一个串行输出

(Q7’),和一个异步的低电平复位,存储寄存器有一个并行8位的,具备三态的总线输出,当使

能 OE时(为低电平),存储寄存器的数据输出到总线。

74HC595各个引脚的功能:

Q1~7 是并行数据输出口,即储寄存器的数据输出口

Q7' 串行输出口,其应该接SPI总线的MISO接口

STcp 存储寄存器的时钟脉冲输入口

SHcp 移位寄存器的时钟脉冲输入口

OE的非 输出使能端

MR的非 芯片复位端

Ds 串行数据输入端

程序说明:

每当spi_shcp上升沿到来时,spi_ds引脚当前电平值在移位寄存器中左移一位,在下一个上升沿到来时移位寄存器中的所有位都会向左移一位,

同时Q7'也会串行输出移位寄存器中高位的值,

这样连续进行8次,就可以把数组中每一个数(8位的数)送到移位寄存器;

然后当spi_stcp上升沿到来时,移位寄存器的值将会被锁存到锁存器里,并从Q1~7引脚输出 参考技术C Q0--Q7应该可以悬空,输出是三态门;输入端、复位端、使能端等就不能悬空了,外部信号对其干扰会使其无法正常工作。串入串出/并出移位寄存器,将串行信号变成并行信号,或者串行输出。应该类似74164 参考技术D 4HC595是具有8位移位寄存器和一个存储器,三态输出功能。 移位寄存器和存储器是分别的时钟。数据在SCHcp的上升沿输入,在STcp的上升沿进入的存储寄存器中去。如果两个时钟连在一起,则移位

寄存器总是比存储寄存器早一个脉冲。移位寄存器有一个串行移位输入(Ds),和一个串行输出

(Q7’),和一个异步的低电平复位,存储寄存器有一个并行8位的,具备三态的总线输出,当使

能 OE时(为低电平),存储寄存器的数据输出到总线。

74HC595各个引脚的功能:

Q1~7 是并行数据输出口,即储寄存器的数据输出口

Q7' 串行输出口,其应该接SPI总线的MISO接口

STcp 存储寄存器的时钟脉冲输入口

SHcp 移位寄存器的时钟脉冲输入口

OE的非 输出使能端

MR的非 芯片复位端

Ds 串行数据输入端

74HC595并行转串行级联芯片学习记录

1 芯片的作用

输入:串行数据

输出:并行数据或串行数据

可以将一路串行数据转换成多路并行数据;

芯片可以进行级联,这样使得一路串行数据转换成更多的并行数据,

达到一个输出引脚控制多路设备的效果。

例如一个引脚控制多个LED灯。

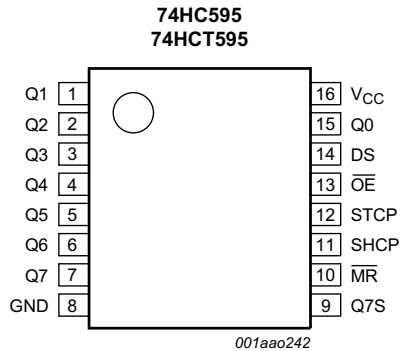

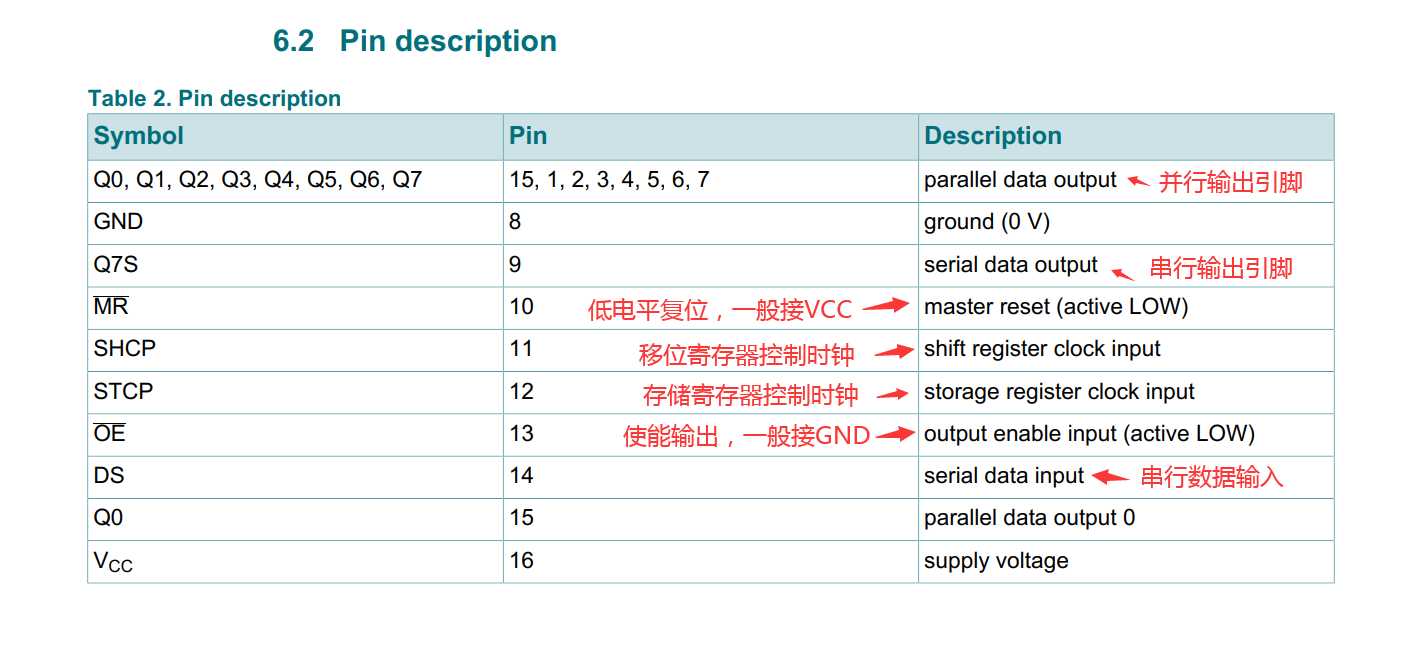

2 芯片引脚介绍

引脚图如下图所示。

引脚说明如下图所示。

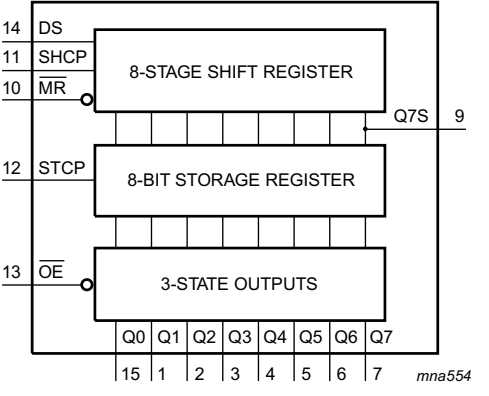

芯片结构图如下图所示,可以看出芯片有两个寄存器,一个移位寄存器,另一个存储寄存器。

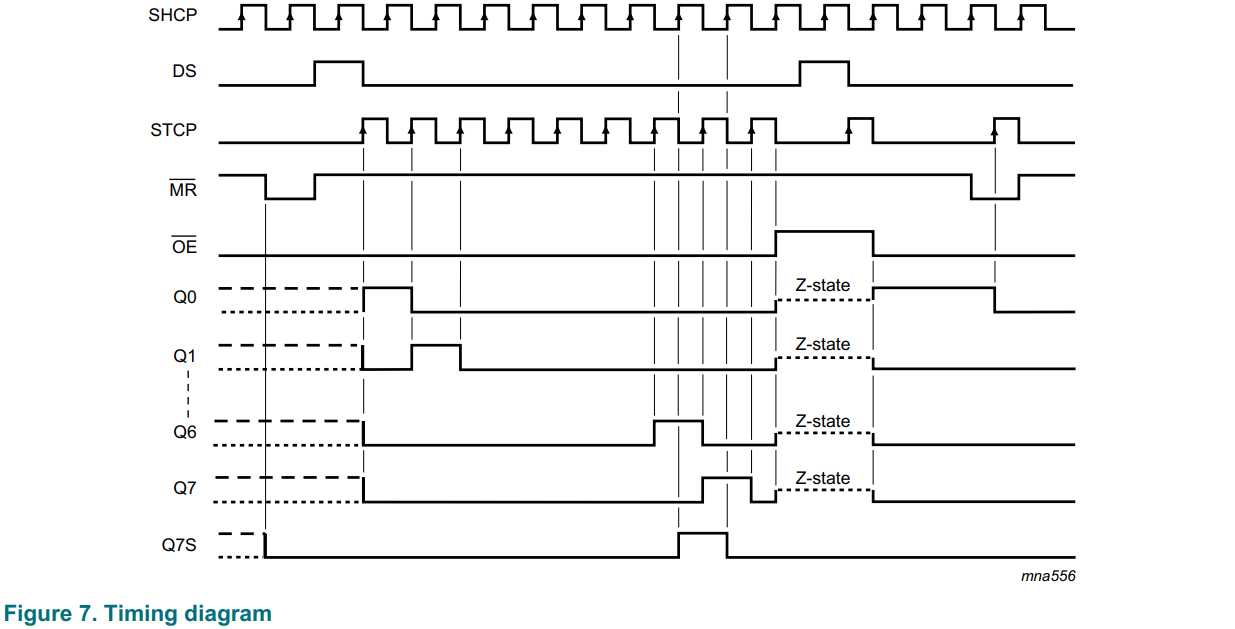

芯片的时序图如下图所示,可以看出第一个数据先进入Q0,一个时钟过后就到达Q1了。

3 芯片的使用

(1)通过控制SHCP产生上升沿,让串行数据不断从DS引脚进行输入,

SHCP每产生一个上升沿,输入一位串行数据。

若超过8位数据,就会从Q7S引脚溢出。

(2)让STCP产生上升沿,数据从移位寄存器转移至存储寄存器。

(3)将OE非引脚置为低电平,数据就输出了。

4 参考

74HC595级联介绍篇(一)

https://blog.csdn.net/k1ang/article/details/80012686

以上是关于74hc595存储寄存器引脚是否可以悬空?他的原理是否让数据暂停?的主要内容,如果未能解决你的问题,请参考以下文章

在线仿真Arduino UNO+74HC595流水灯 + 按键控制