典型MOSFET制造工艺流程示意图

Posted 硬件老钢丝

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了典型MOSFET制造工艺流程示意图相关的知识,希望对你有一定的参考价值。

复旦大学姜玉龙的课程-半导体器件(截图,图中有的红点是鼠标)

下面将阐述这个工艺过程。

硅片基底,假设厚度800um,实际上只有上表层有用大概10um厚度左右

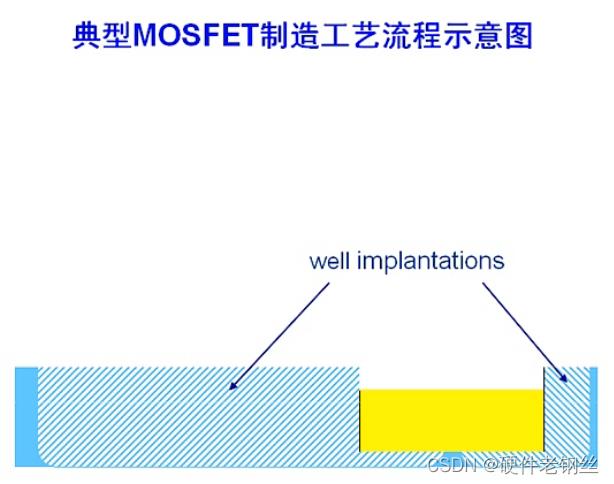

然后填充氧化物,用来隔离

然后进行阱注入,可以选择两边分别注入N阱或者P阱。从而隔开NMOS和PMOS。

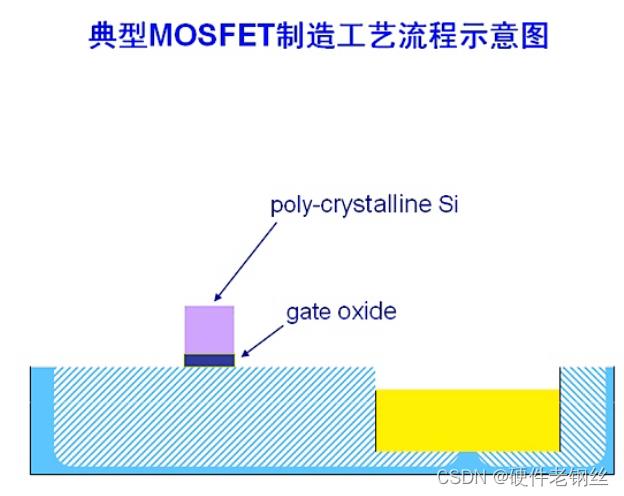

做晶体管,大面积氧化,MIS,用重掺杂的多晶硅,然后进行刻蚀,得到下面的图。

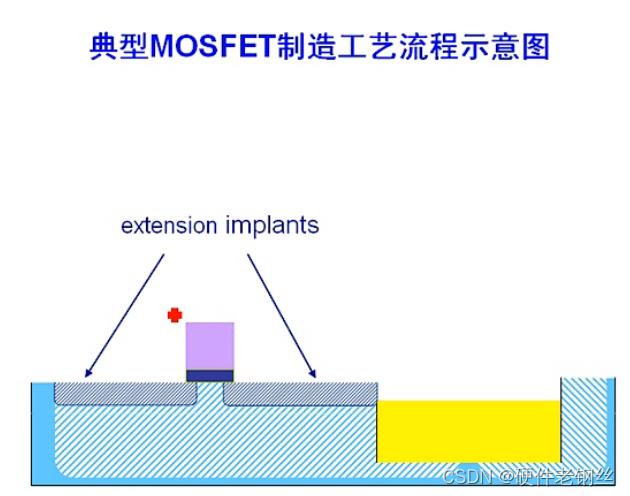

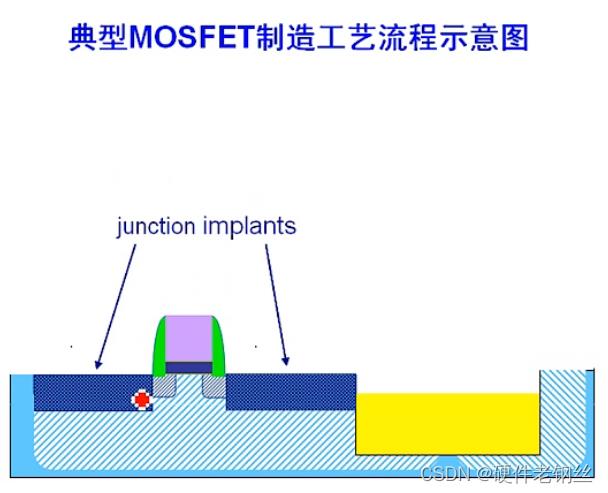

常规的晶体管只有一个源和漏,为了减轻现在晶体管横向变小后造成的电场过强的问题,热电子现象很明显,为了使得电场强度降下来,就得使得源和漏的掺杂降低,在PN结里,耗尽层一般是在轻掺杂那边,重掺杂那边不承担什么电压。换句话说,相同的电压,如果把PN结两边电压降低,那么他的峰值电场一定是下降的,相当于耗尽层电场降低。常规都是N+PN+,所以直接原来的掺杂降低,但是电阻大,也不行,不能把导通的压降都放在源和漏上,一定要在沟道区有有效的压降,所以可以分两步,先低掺杂然后再高掺杂。

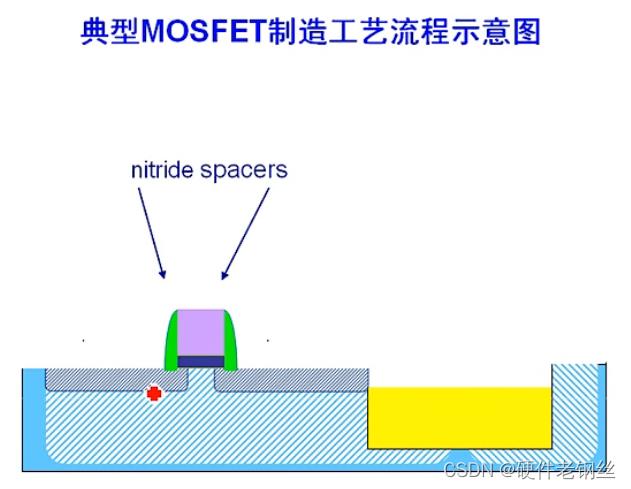

下图,先进行浅注入,

然后在上面填充一层SiN或者Si02,进行定向刻蚀耗掉奠基厚度。旨在纵向方向刻蚀,左右刻不光,最后就会使得栅极两边留下边墙,是绝缘体将栅极保护起来。

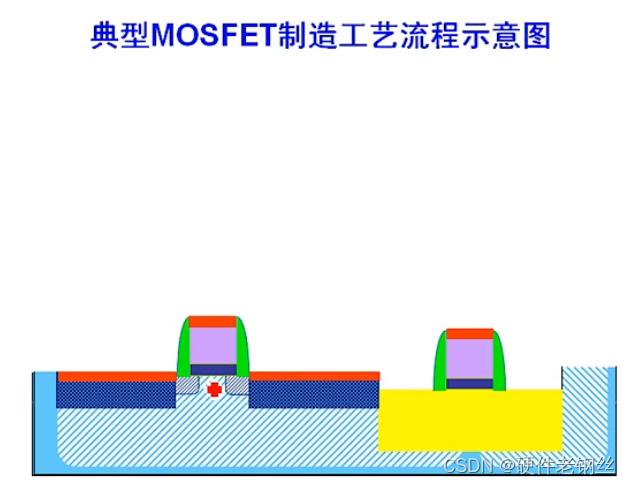

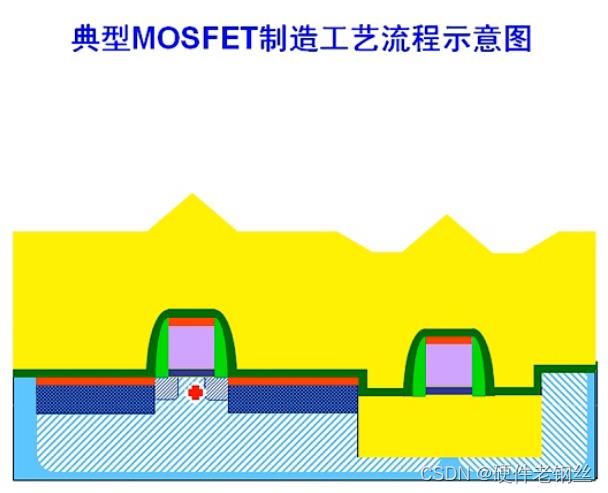

然后重掺杂,自对准,不需要光刻了,例如Nmos,就是N+的栅、漏和源。这样就得到了源、漏和栅极。下图中的灰色部分为真正起作用的源级和漏极,但由于其是浅掺杂,电场被有效降低,可以缓解热电子效应。

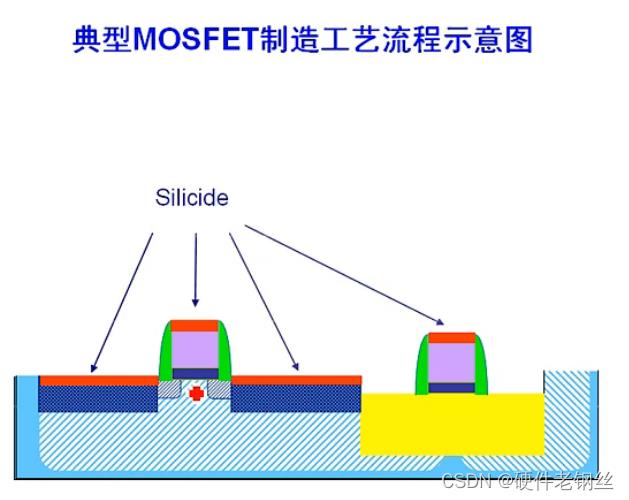

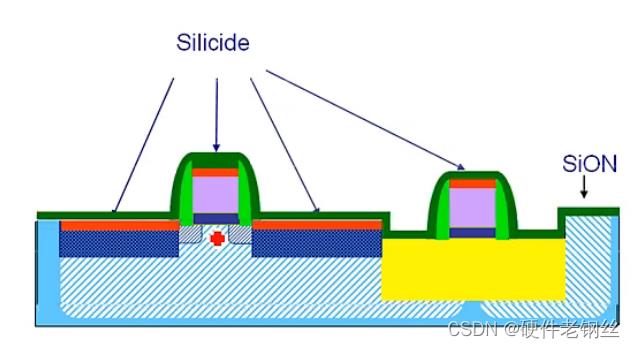

然后做电极,把源漏栅引出来。

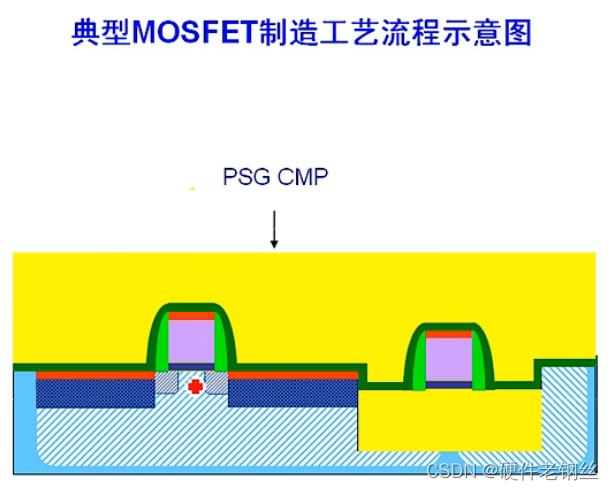

用硼磷硅玻璃封住,使器件钝化

磨平,CMP机械抛光

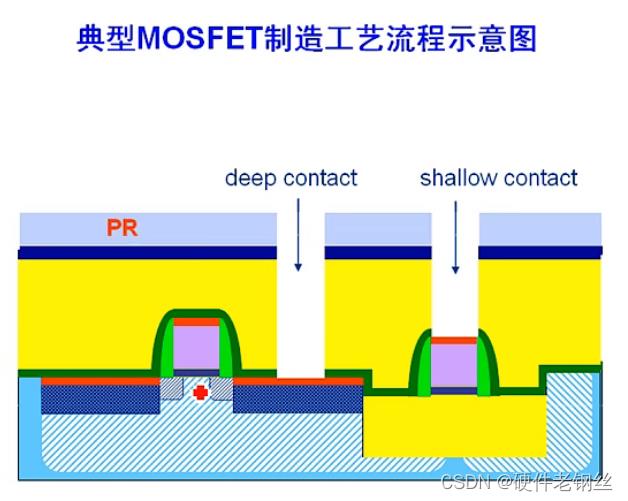

开洞,得到一个典型的NMOS或者PMOS晶体管。

以上是关于典型MOSFET制造工艺流程示意图的主要内容,如果未能解决你的问题,请参考以下文章