system generator基于system generator的整数除法器设计

Posted fpga&matlab

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了system generator基于system generator的整数除法器设计相关的知识,希望对你有一定的参考价值。

目录

1.软件版本

MATLAB2013b,ISE14.7

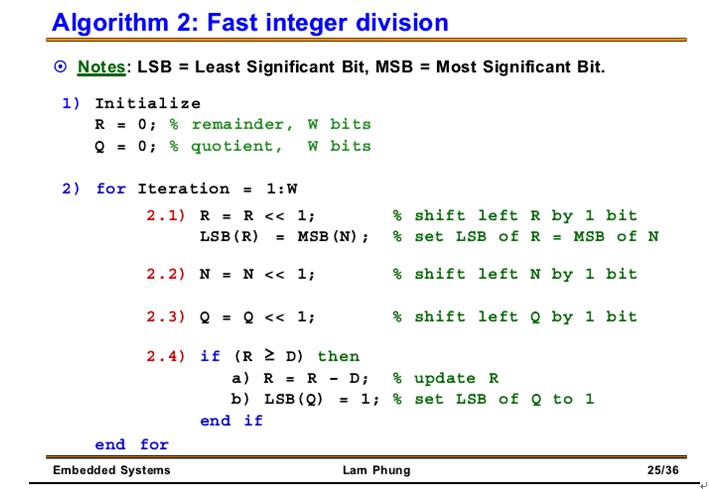

2.本算法理论知识点

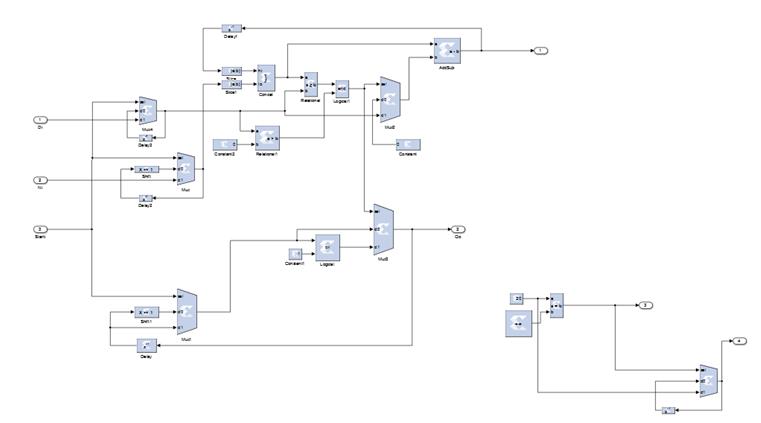

system generator,simulink,ISE的联合使用。

3.算法具体理论

4.部分核心代码

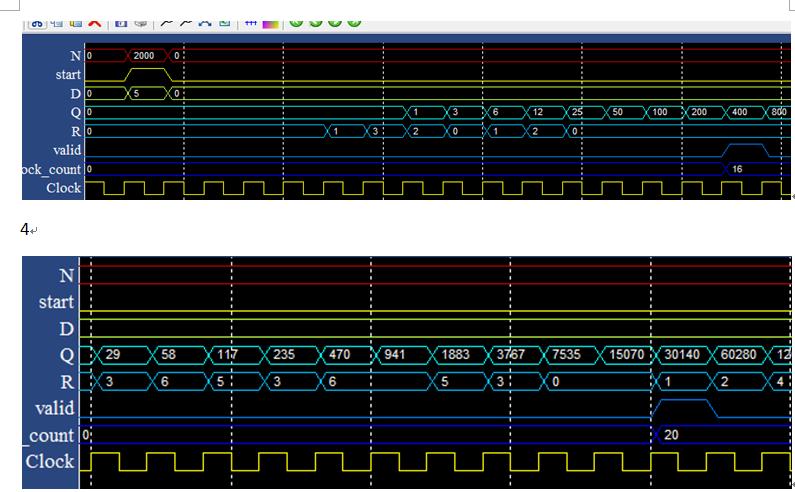

5.仿真演示

6.本算法写论文思路

这个课题要求设计一个高速的FPGA整数触发器,

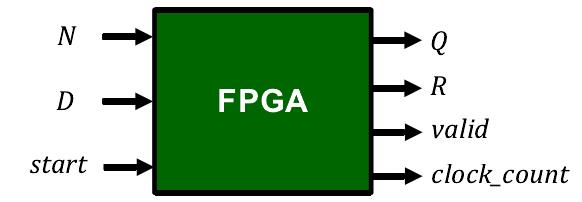

1.有三个输入信号N,D,START

2.信号N和D为无符号整数,N和D的位宽为W,W是一个参数,从对应的simulink文件中看到,可以设置为8,10,20,32等。

3.信号start为布尔型参数,1的时候,开始计算,在计算完成之前,start不会再次产生高电平。

4.输出有四个,Q,R,Valid和clockcount

5.Q是商,R为余数,位宽均为W,

6.当计算完成后,valid输出1,

7,输出信号clockcount需要时钟个数,例如,计算开始第二周期开始计算,第20周期完成,那么clockcout为18.

8.设计必须使用matlabsimulink和xilinx中的SG模块,如下模块不能被使用:

7.参考文献

[1] Christe A , S. An efficient FPGA implementation of MRI image filtering and tumor characterization using Xilinx system generator[J]. International Journal of Vlsi Design & Communication Systems, 2012, 2(4):95-109.

8.相关算法课题及应用

无

A40-01

以上是关于system generator基于system generator的整数除法器设计的主要内容,如果未能解决你的问题,请参考以下文章

基于MATLAB System Generator 搭建Display Enhancement模型

基于System Generator的1024QAM-FM软件无线电联合调制解调系统的FPGA实现