Multimedia

Posted 四季帆

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了Multimedia相关的知识,希望对你有一定的参考价值。

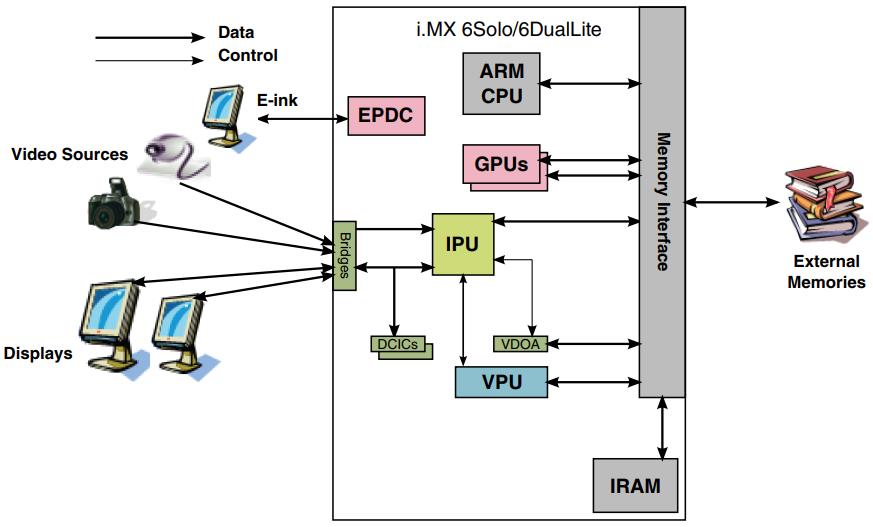

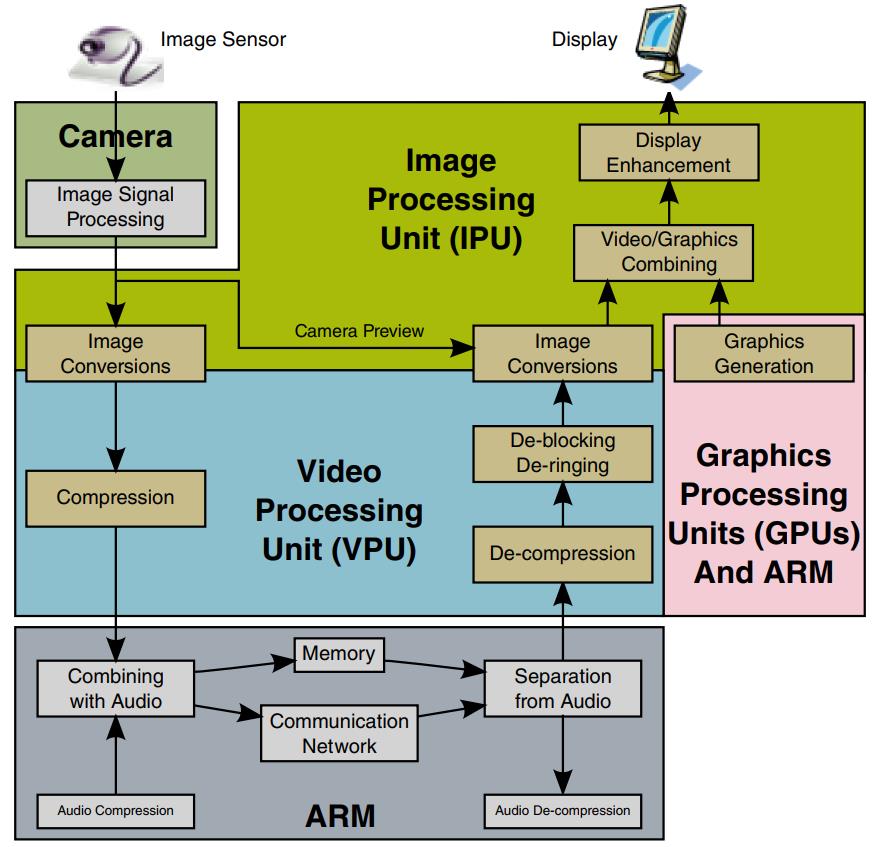

9.1 Video Graphics Sub System

芯片视频图形子系统由以下专用模块组成:

1. 视频处理单元(VPU):多标准高性能视频/图像编解码器;

2. 两个图形处理单元(GPUs):

3D GPU:加速3D图形的生成(OpenGL/ES);

2D GPU:加速2D图形的生成。

3. 一个图像处理单元(IPU):提供摄像头和显示器的连接,相关的处理,同步和控制。

4. 显示接口的桥梁:提供从IPU支持的数字显示接口到其他接口的可选转换:

LVDS bridge (LDB): providing up to one LVDS interface

HDMI transmitter

MIPI/DSI transmitter

5. MIPI/CSI-2 receiver

6. 使用两个(相同的)显示内容完整性检查程序(DCIC)对显示的敏感数据进行身份验证。

7. 一种视频数据顺序适配器(VDOA):用于将视频数据从VPU使用的“平铺”顺序重新排序为IPU所需的传统光栅扫描顺序。

i.MX 6Solo/6DualLite视频/图形系统的高级集成方案如下图所示。

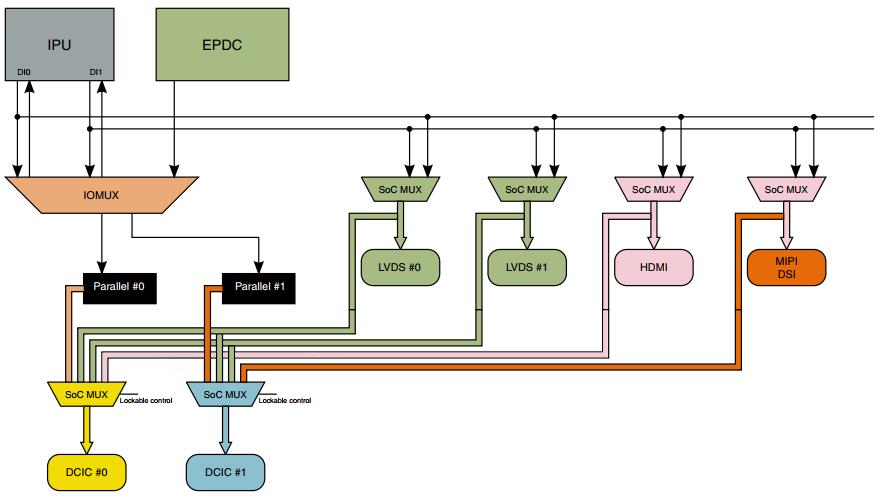

9.1.1 Display outputs

i.MX 6Solo/6DualLite在两个显示端口(每IPU 2个)上实现了一个健壮的多路复用逻辑,与外部接口(直接或通过桥接(MIPI、LVDS、HDMI)),具体描述如下:

1>两个显示端口直接被IPU并联驱动;像素时钟至少高达200mhz(外部负载高达10pf)。

并行接口工作频率高达200mhz;

HDMI接口工作频率高达270mhz。

2>两个LVDS通道,由LDB驱动;像素时钟高达170MHZ。

3>1个HDMI端口,由HDMI发射器驱动,像素时钟高达270mhz(由IPU功能门控)。

4> 一个MIPI/DSI端口,由MIPI/DSI发射器驱动,2个1GHZ的数据通道。

5> IPU display port (DI)可分别连接到上述各端口。

6> IPU有2个显示端口,最多两个外部端口可以在任何给定的时间是活跃的。(额外的异步数据流可以通过并行端口和MIPI/DSI端口发送。)

7>支持的读通道如下:

对于Parallel0端口:通过DI0;

对于Parallel1端口:通过DI1。

8>任何一个DCICs的输入都是从下列总线之一获取的

对于每个并行接口:探测I/O环回(本质上相当于探测外部电线);

对于其他集成接口(例如LVDS):探测IPU的DI1输出(本质上相当于序列化器的输入);

对于数据使能信号,从上述各总线探测两个控制信号。

i.MX 6Solo/6DualLite还实现了电子墨水显示的EPDC。

显示信号路由的可视化视图如下图所示。芯片MUX选择信号由在IOMUXC_IOMUXC_GPR寄存器描述字段中的IOMUX控制器(IOMUXC)章节中指定的配置位驱动。

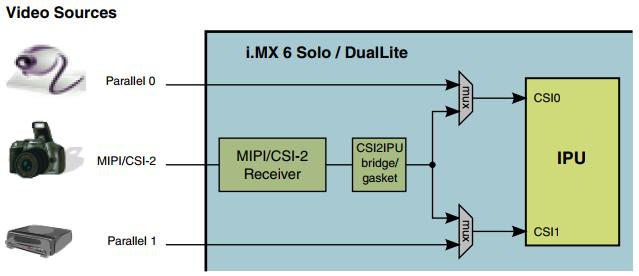

9.1.2 Video input

有2个视频输入端口(例如从图像传感器),详见下图。

其中一个并口直接连接到IPU输入口。

一个MIPI/CSI-2端口- IPU每个周期接收两个components从MIPI_CSI2接口。接口的最大带宽如下所示:

250M字节每秒,2数据通道配置(1000Mbps/lane);

125M字节每秒,1数据通道配置(1000Mbps/lane)。

IPU有两个输入端口CSI0和CSI1,可以同时独立接收数据。在任何给定的时间,一个IPU输入端口可以从一个并行的外部端口或从MIPI/CSI-2接收器接收数据。

MIPI/CSI-2端口最多可以接收4个并发数据通道。每个数据通道可以通过IPU的两个CSI端口中的一个进行路由。像素数据可由IPU进一步处理。其他类型数据可以通过CSI透明地作为通用数据传输到系统内存。

IPU、VPU、VDOA和gpu都有主AXI接口,提供对系统内存的访问。

模块控制方式如下(由ARM CPU或SDMA控制):

1.LDB由连接到顶级寄存器的信号控制。

2.所有其他模块都有一个主机接口。对于VPU, VDOA和DCIC,这是一个从IP端口,对于MIPI 桥,gpu和ipu,这是一个从AHB端口。

3.VPU、VDOA、gpu和IPU之间的数据流通过系统内存,通常由CPU控制。对于空间情况,提供了直接同步接口;

4.IPU和VPU之间的接口,用于低时延视频录制。

5.VDOA和IPU之间的接口,用于从VDOA通过IRAM将数据紧密地流水线到IPU。

9.1.3 同步机制

i.MX 6Solo/6DualLite提供了IPU和VPU之间以及IPU和VDOA之间的HW同步机制,以减少核心干预并实现锁步操作。

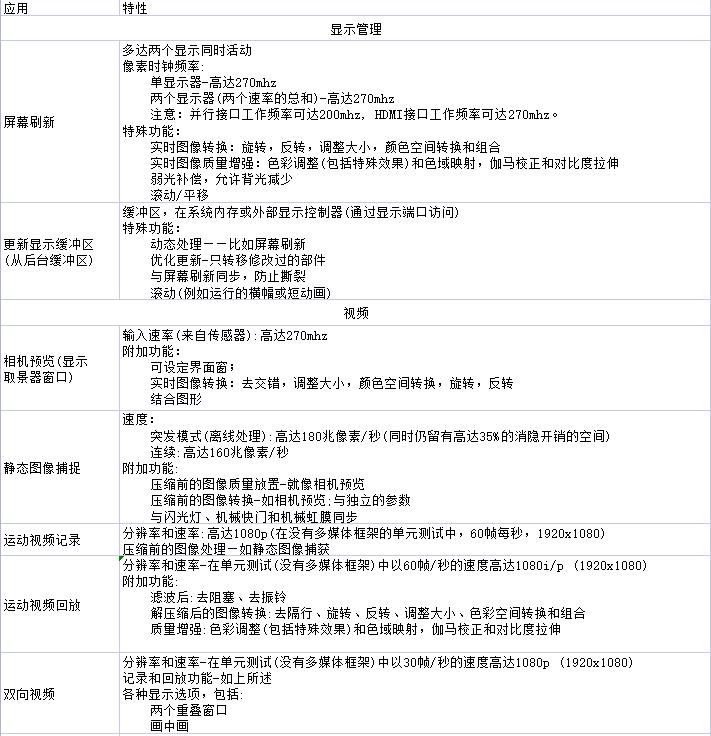

9.1.4 支持应用程序

上面描述的系统支持各种视频/图形应用。下表描述了主要的应用程序。

下图是多媒体应用程序的处理流程示例。

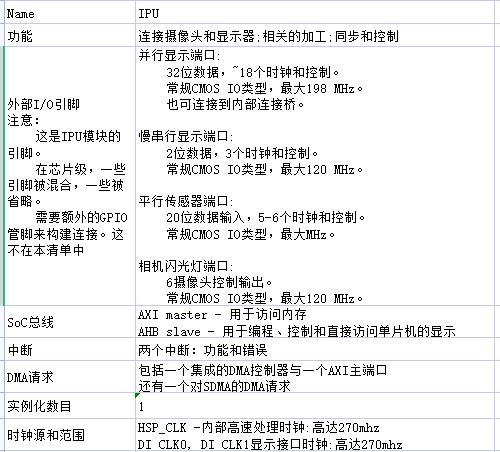

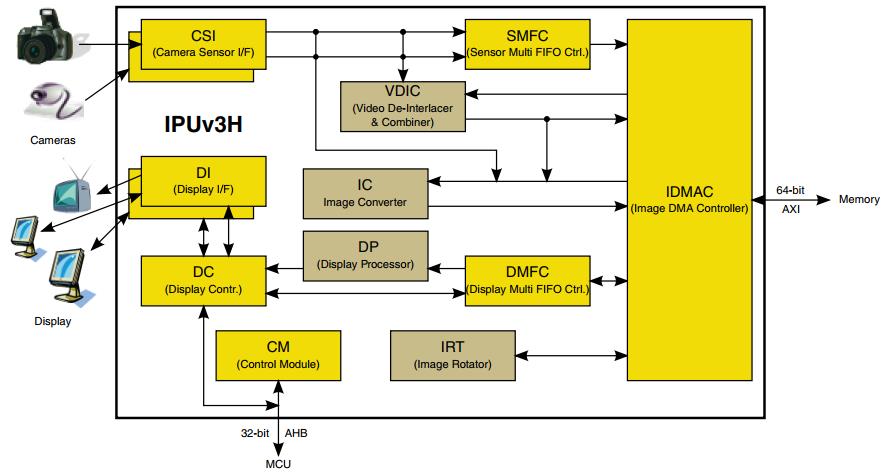

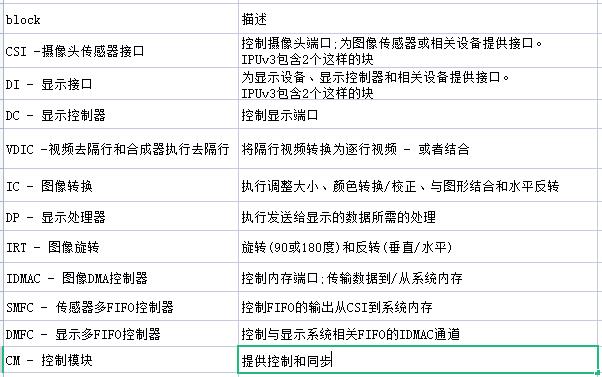

9.2 Image Processing Unit(IPU)

IPU IP参数说明如下表所示

IPU的目标是为从图像传感器和/或到显示设备的数据流提供全面支持。这项支助包括这些活动的所有方面:

连接到相关设备-摄像机,显示器,图形协处理器,电视编码器和解码器。

相关的图像处理和操作:图像增强和转换等。

同步和控制功能(例如,避免撕裂工件)

这种综合方法带来了几个显著的优势:

自动化:减少了单片机(主控单元)对图像管理的介入。特别是,显示刷新/更新和摄像头预览(显示来自图像传感器的输入)可以完全自主地执行。由此带来的好处是减少了由于SW-HW同步带来的开销,释放了MCU去执行其他任务,并降低了功耗(当MCU空闲时,可以关机)。

最优数据路径:最小化对系统内存的访问。特别是,当从图像传感器接收数据和/或向显示器发送数据时,可以实时执行重要的处理。系统内存基本上只在需要改变像素顺序或帧率时使用。由此产生的好处是减少了系统总线上的负载,并进一步降低了功耗。

资源共享:最大限度的重用HW为了不同的应用程序,从而以最少的硬件支持广泛的需求。

上面提到的硬件重用是通过每个硬件块的复杂可配置性实现的。这种可配置性还允许支持广泛的外部设备、数据格式和操作模式。

下图给出了一个简化的IPU 块框图。

下表描述了每个块的作用。

9.2.1 IPU外部端口

IPU有以下接口:

两个摄像头端口-由CSI模块控制-提供与图像传感器和相关设备的连接。

两个显示端口 - 每个由一个DI模块控制 - 提供与显示器和相关设备的连接。

内存端口- AXI (AHB V3.0)主,由IDMAC控制-提供到系统内存的连接。

AHB-lite从端口,提供与ARM MCU的连接(以及与任何其他连接到ARM的cross-ba开关的主端口)

9.2.1.1 摄像头端口

这些端口的作用是接收来自视频源(例如图像传感器)的输入,并为相机的时间敏感控制信号提供支持。(非时间敏感的控制-例如配置,复位-由MCU通过I2C I/F或GPIO信号执行)。

每个摄像头接口包括以下特点:

直接连接到大多数相关的外部设备。

并行接口-多达20位数据总线

帧大小:高达8192 x 4096像素(包括空白间隔)

支持的数据格式包括Raw (Bayer), RGB, YUV 4:4:4, YUV 4:2:2和灰度,每个值(组件)高达16位。

同步-视频模式

传感器是像素时钟(PIXCLK)和同步信号的主控

接收同步信号的方法如下:

专用控制信号-VSYNC,HSYNC-可编程脉冲宽度和极性

嵌入在数据流中,松散地遵循BT.656协议,在代码值和位置方面具有灵活性。

同步-静止图像捕捉

图像捕捉由MCU或外部信号(如机械快门)触发

同步闪光灯产生多达6个输出-传感器和相机外围设备(闪光灯,机械快门…)

附加功能

通过周期性跳过帧来降低帧率

缩小x2,跳过行/列

Window-of-interest选择

预闪光-用于减少红眼和在弱光条件下测量(例如聚焦)

几个传感器可以连接到每一个CSI的。同时支持的功能(发送数据)如下:

可以通过不同的CSI分别接收两个流。

只有一个流可以传输到VDIC或IC进行实时处理,而另一个流可以直接发送到系统内存。

摄像头接口支持的输入速率如下:

峰值:高达240mhz(值/秒)

平均(假设35%的空白开销),YUV是4:2:2

一个周期的像素(例如BT.1120):高达180 MP/sec,例如12M像素@ 15fps

两个周期的像素(例如BT.656):高达90 MP/sec,例如6M像素@ 15 fps。

动态处理可能被限制在一个较低的输入速率-见下文。

9.2.1.2 显示端口

这些端口的作用是与显示设备通信,可以直接或通过控制器(如图形加速器)或桥接器(如电视编码器或LVDS接口桥接器)。

9.2.1.2.1 访问模式

支持两种访问模式:同步访问和异步访问

9.2.1.2.2 同步访问

在这种模式下,IPU向显示设备传输一个二维像素块,与屏幕刷新周期同步。

该模式具有双重作用:

对于没有ram的显示器或电视屏幕,此模式用于从系统内存中的显示缓冲区执行屏幕刷新过程。

对于“智能”显示器,这种模式用于将矩形像素块转移到显示器的屏幕上,在某些情况下,还可以转移到显示缓冲区。

在这两种情况下,IPU向显示器发送所有控制屏幕刷新的同步信号,块传输与这些信号同步。这种同步意味着在使用此模式时避免了撕裂效果。

9.2.1.2.3 异步访问

这是用于与外部显示控制器(可能在智能显示器或图形加速器中)通信的主要模式。在此模式下,IPU对控制器的内存和寄存器进行随机读写。

提供了以下访问类型:

在IPU中进行实时处理后,将数据传输到外部设备。

数据传输(DMA) -读/写-在主机的系统内存和外部设备之间,通过IPU的内存端口(由IDMAC控制);例如,转移一个矩形像素块(可能是全屏)

主机访问-读/写-到外部设备,通过AHB-slave端口

9.2.1.2.4 接口细节

显示接口非常灵活,支持主流厂商的各种设备。

提供了以下接口类型(在两个显示端口中):

一个并行视频接口(用于同步访问)-多达24位数据总线。

支持8位BT.656和16位BT.1120协议

支持HDTV标准SMPTE274 (1080i/p)和SMPTE296 (720p)

一个并行双向总线接口(用于异步访问)- 32位数据总线。

串行接口 - 3线、4线和5线(两种类型)(用于异步访问)

支持的像素数据格式为:RGB和YUV 4:2:2。

对于接口时钟,有以下选项(对于每个端口独立)

从IPU内部时钟派生(主模式)

由外部源提供(从模式

支持的传输速率

当单个端口处于活动状态时,像素时钟速率最高可达198mhz

当两个端口都处于活动状态时

每个像素时钟速率可达MHz

像素时钟速率的总和可达MHz

9.2.1.2.5 连接显示设备

IPU可以连接多个显示设备。

特别地,它支持以下设置:

主要的液晶显示器。

第二个液晶显示器。

外部显示;例如电视。

以上设备的同时功能可以通过以下方式实现:

可以(同步或异步)独立地访问两个设备,每个设备都通过一个不同的端口:每个设备都 使用任何可用的接口。

两个设备可以通过传统的串行和并行接口,使用CS信号分时异步访问。

9.2.2 处理

IPU处理矩形块的像素。处理过程由四个模块完成:VDIC、IC、DP和IRT。

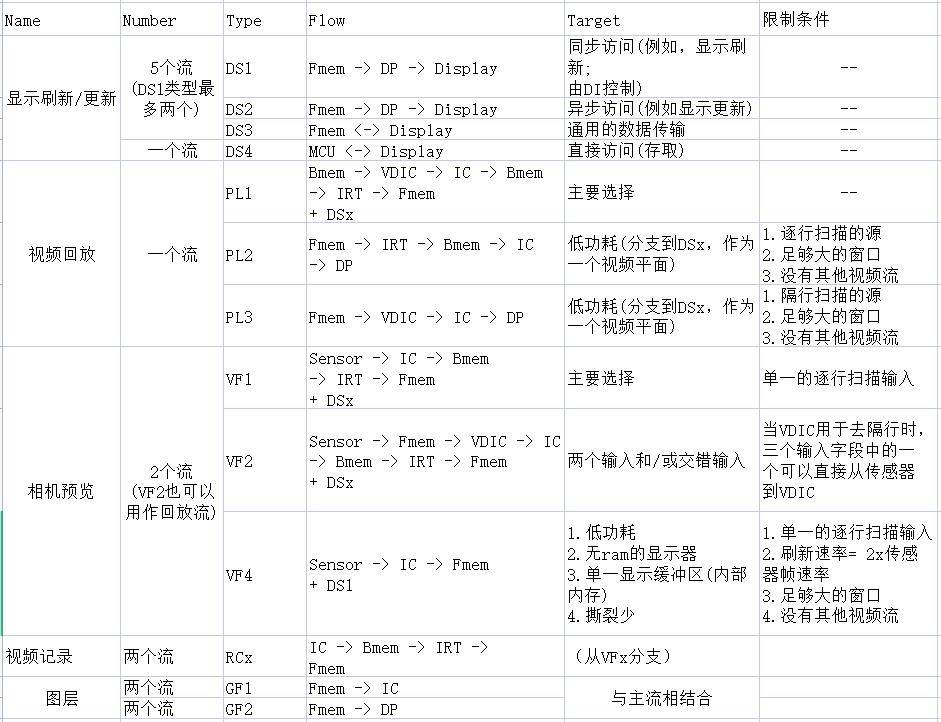

支持几种分时数据流,如下表所示。

9.2.2.1 显示处理(DP)

显示处理器执行发送到显示器的数据所需的所有处理。

结合2个视频/图形平面

覆盖一个简单的HW光标32 x 32像素,颜色一致;可以与背景逻辑结合。

颜色转换/校正-线性(乘法和加法)可编程;

包括:

YUV<-> RGB, YUV<->YUV转换,其中YUV表示MPEG-4标准中定义的任何一种颜色格式

调整:亮度,对比度,色彩饱和度…

特效:灰度等级,颜色反转,sephia,蓝色色调…

保持色调的色域映射为最小的颜色失真

应用于组合的输出或一个输入

伽马校正和对比拉伸-可编程分段线性映射

DP在任何给定的时间处理单个数据流,但它最多支持三个数据流,通过时间共享,其中一个可能是同步的。

数据速率高达198M像素/秒

9.2.2.2 视频去隔行(VDIC)

VDIC是视频去隔行和合并模块,有两种工作模式:

去隔行:将隔行视频流转换为逐行视频流。

组合: 将两个视频/图形平面和一个背景色组合在一起。

VDIC的输入和输出如下:

去隔行输入:三个连续的字段

Source:

最近的字段可能来自CSI或系统内存

另外两个字段从内存中读取

Field size:支持高达1080p

像素格式:YUV 4:2:2/4:2:0, 8 bits/value

典型的视频源:SDTV: 480i30 (720x480 at 30 fps) or 576i25 (720x576 at 25 fps) and HDTV: 1080i30 (1920x1080 at 30 fps)

输入的组合:两个逐行视频/图形平面

Source:系统内存

Plane size:高达1920x1200像素。

像素格式:RGB/YUV 4:2:2, 8 bits/value

输出:逐行的画面(帧)

目标:到系统内存或到图像转换器。

帧大小:高达1920x1200像素。

速率:高达198M像素/秒。

格式:与输入格式相同。 去隔行使用高质量的3场滤波器,这是运动自适应:

对于慢动作 - 保留完整的分辨率(顶部和底部字段)

对于快速运动 - 防止运动伪影

VDIC在任何给定时间都支持单个视频流。

9.2.2.3 图像转换(IC)

图像转换器在视频流上执行各种操作。

执行的操作包括:

调整大小:

完全灵活的缩放比最大缩小比:8:1。受此限制,任何N->M大小的调整都可以执行

独立的水平和垂直调整比例。

颜色转换/校正-线性(乘法和加法)可编程;

包含:

YUV<-> RGB, YUV<->YUV转换,其中YUV表示MPEG-4标准中定义的任何一种颜色格式

调整:亮度,对比度,色彩饱和度…

特效:灰度,颜色反转,sephia,蓝调

与图形平面结合(例如特定于应用程序的覆盖)

水平反转 IC支持三种分时数据流:记录、摄像头预览和回放(前两种共享一个共同的输入)。

支持的帧分辨率高达4096x4096的输入和1024x1024的输出。更宽的帧可以通过将它们分割成垂直条纹来进行处理。

数据吞吐量:

对于单个活动任务:输入最多240M像素/秒,输出最多120M像素/秒。

对于多个活动任务:输入高达200M像素/秒,输出高达100M像素/秒。

9.2.2.4 图像旋转(IRT)

图像旋转器执行以下任意组合:

90度旋转

水平反转

垂直反转

数据吞吐量:

当单个任务处于活动状态时:最高可达120M像素/秒。

当更多的任务是活跃的:高达100M像素/秒。

9.2.3 自动程序

IPU配备了强大的控制和同步功能,以最小的ARM参与和最小的内存使用执行其任务。

特别是,它包括:

一个集成的DMA控制器与一个AXI主端口,允许自主访问系统内存。

一个集成的显示控制器,执行无ram显示的屏幕刷新。

翻页双缓冲机制,同步读和写访问系统内存,以防止撕裂效应。

带有视频/图形源的双/三重缓冲同步机制。

内部同步,例如,从传感器输入和输出到显示之间的同步。

因此,在大多数情况下,只有当MCU也执行部分处理(如视频编码)时,它才会参与。特别是,以下程序由IPU完全自主执行:

无ram显示的屏幕刷新

相机预览(显示取景器-从图像传感器到显示器的视频流)。

Note:当源和目的地的帧速率相同时,直接摄像机显示流是可能的(通常目标显示将是异步显示,其中显示以源的速率更新)。

通常,在一段较长的时间内,系统中没有其他活动。MCU处于空闲状态,可调至低功耗模式,降低功耗,显著延长电池寿命。

IPU支持几种技术进一步降低显示系统的功耗:

动态背光控制,通过图像增强实现弱光补偿

自动程序更多的特点和功能包括:

自动显示一个变化的图像(动画)或移动的图像(滚动)。

显示更新的时机可以调整,避免撕裂。

来自图像传感器的视频流可以直接发送到用于屏幕刷新的显示缓冲区,同时避免撕裂。

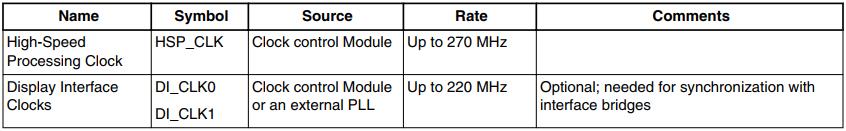

IPU收到的时钟源如下表所示。

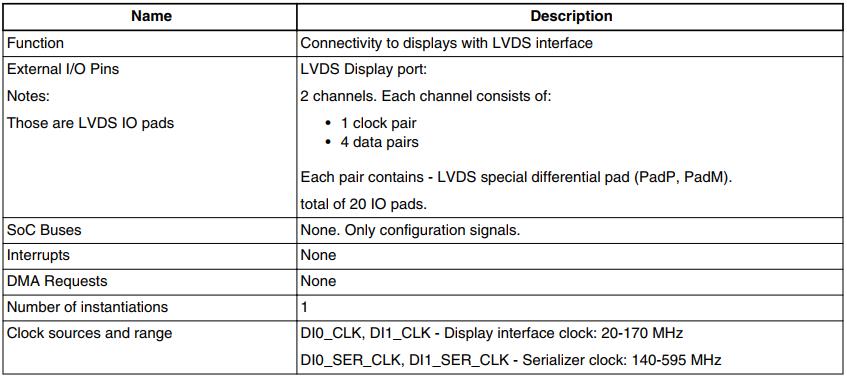

9.3 LVDS显示桥(LDB)

LVDS显示桥(LDB)将用于连接IPU(图像处理单元)到外部LVDS显示接口。

9.3.1 LDB概述

LDB的目的是通过LVDS接口支持从IPU到外部显示设备的同步RGB数据流。这项支持包括这些活动的所有方面:

与相关设备的连接-带有LVDS接收器的显示器。

按照外部显示接收机的要求和LVDS显示标准进行数据整理。

同步和控制能力。

9.3.2 LDB外部端口

LDB包含以下端口:

两个输入并行显示端口。

两个输出LVDS通道-每个通道由4个数据对和1个时钟对组成(对=LVDS pad包含PadP, PadM)。

控制信号-配置LDB参数和操作。

来自SOC锁相环的时钟。

9.3.3 输入并行显示端口

支持一个或两个(DI0, DI1)并行RGB输入端口(可配置)。仅支持同步访问方式。

每个RGB数据接口包含以下内容:

18位或24位的RGB数据

像素时钟

控制信号:HSYNC, VSYNC, DE,和1个额外的可选通用控制。

每个像素时钟周期传输的数据接口总计多达28位。

速率支持:

对于双通道输出:高达170 MHz像素时钟(例如UXGA - 1600x1200 @ 60 Hz + 35%消隐) 单通道输出:每个接口高达85 MHz。(例如:WXGA - 1366x768 @ 60hz + 35%消隐)。

9.3.3.1 LVDS输出端口

有2个LVDS通道。这些输入通过LVDS接口或LVDS接收器与外部LCD显示器通信(通信内容为RGB数据和控制数据)。

LVDS端口的使用方式如下:

一个单通道输出

单路双路输出:单路输入,分割为两个输出通道

两个相同的输出:单个输入发送到两个输出通道

两个独立的输出:两个输入分别发送到不同的输出通道

9.3.3.2 控制信号

控制信号用于配置LDB操作。

9.4 视频数据顺序适配器(VDOA)

VDOA的目标是将视频数据从VPU使用的“平铺”顺序重新排序为IPU需要的传统光栅扫描顺序。

9.5 显示内容完整性检查(DCIC)

DCIC的目标是验证发送到显示器的安全关键信息没有损坏。

为了符合ASIL B(汽车安全完整性等级B)规范,汽车仪表组中的警告图标必须进行这种验证。它也需要在其他安全敏感系统。

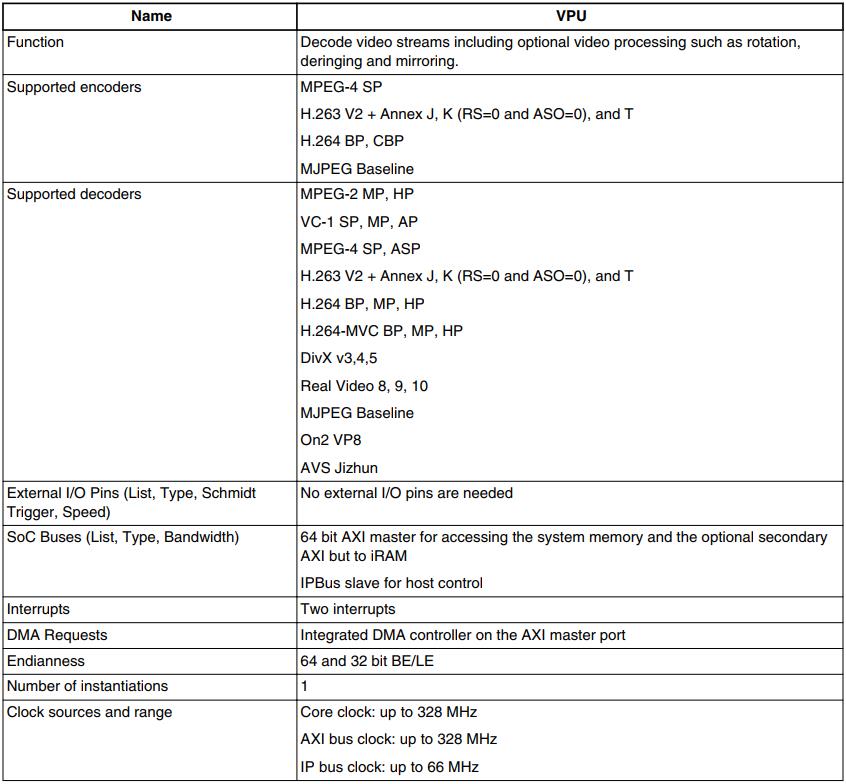

9.6 视频处理单元(VPUv6)

VPU是一个多标准的视频编解码器(编码器/解码器),能够通过时间复用同时处理多个流。

它是一个非常灵活的块,由硬件加速器围绕一个可编程核心组成。VPU向系统提供了一个由嵌入式处理器控制的寄存器映射接口。终端用户只能使用每个BSP程序员用户指南提供的API与VPU进行交互。此API将用户与寄存器接口层可能发生的更改隔离开来。

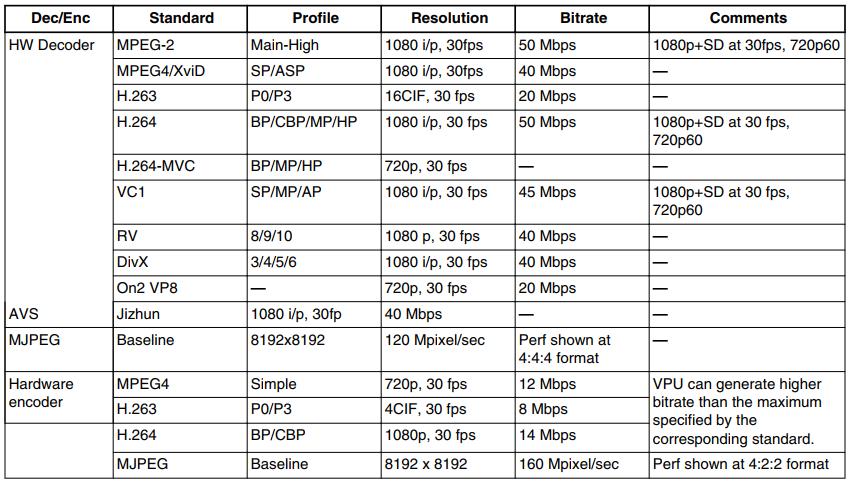

在下表中,我们可以看到VPU规格的概要。VPU有自己的DMA驱动的AXI主机,允许它直接从系统内存(DDR和iRAM)检索所需的数据。主机ARM平台中的负载可以忽略不计,因为它只需要在帧级与VPU交互。

NOTE:在i.m x6系列处理器上,RealNetworks视频编解码器默认禁用。详情请与您的FSL销售代表联系。

i.MX 6Solo/6DualLite处理器具有高性能视频处理单元(VPU),其中包括许多标准和高清晰度视频解码器和编码器,作为一个多标准视频编解码器引擎,以及几个重要的视频处理,如旋转和镜像。

9.6.1 基础结构

VPU是自包含的,除了内存访问。它通过两个AXI主端口连接到内存子系统。ARM通过IP总线配置VPU操作,该IP总线在垫圈中转换为APB。

增加了一个新功能,允许VPU编码帧,即使IPU只写入一小部分源视频(从摄像机传感器)到帧缓冲区。这个特性被称为IPU-VPU子帧同步。为了实现这一功能,增加了四个额外的信号,其中三个从IPU到VPU,一个从VPU到IPU。

9.6.2 功能概述

VPU的编码/解码能力如下表所示:

VPU还可以实现以下功能:

实时(90 x n)度同步旋转和镜像(n = 0,1,2,3)。

后加工

MPEG-4的去阻塞过滤

用于MPEG-4和H.264解码器的去振滤波

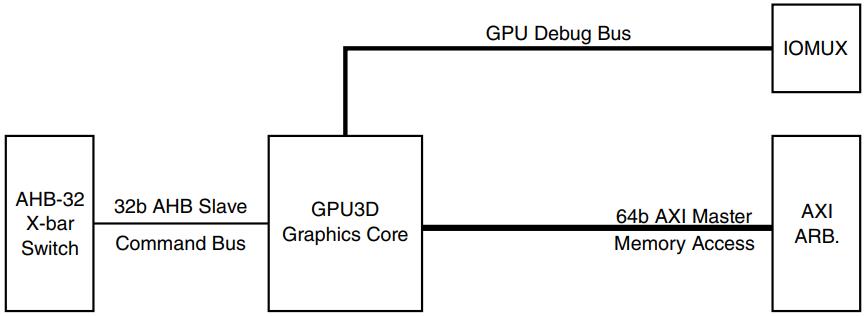

9.7 OpenGL ES 3D图形处理单元(GPU3Dv5)

9.7.1 OpenGL概述

9.7.2 OpenGL的特性

GPU3D的功能概述包括:

符合OpenGL ES 2.0,包括扩展;OpenGL ES 1.1;OpenVG 1.1

IEEE 32位浮点管道

超线程,统一的顶点和碎片着色器

在高和低数据速率下的低带宽

低CPU负载

每个顶点多达12个可编程元素

依赖的纹理操作与高性能

阿尔法混合

深度和模板比较

支持8个碎片着色器同时纹理

支持4个顶点着色器同时纹理

点采样,双线性采样,三线性滤波,立方纹理

决心和快速清晰

8k x 8k纹理大小和8k x 8k渲染目标

9.7.3 OpenGL块框图

9.7.4 OpenGL的性能

GPUv5 @ 532MHz (clock rate TBD)

9.7.5 OpenGL的软件

API / Driver Support

• OpenGL ES 1.1, 2.0, and 3.0 (draft)

• OpenVG 1.1

• EGL 1.4

• OpenVG 1.1

Operating Systems

• Windows CE

• Linux Embedded and X11

• android

9.8 2D图形处理单元(GPU2Dv2)

GPU 的介绍简直就是一笔带过,此处直接省略······

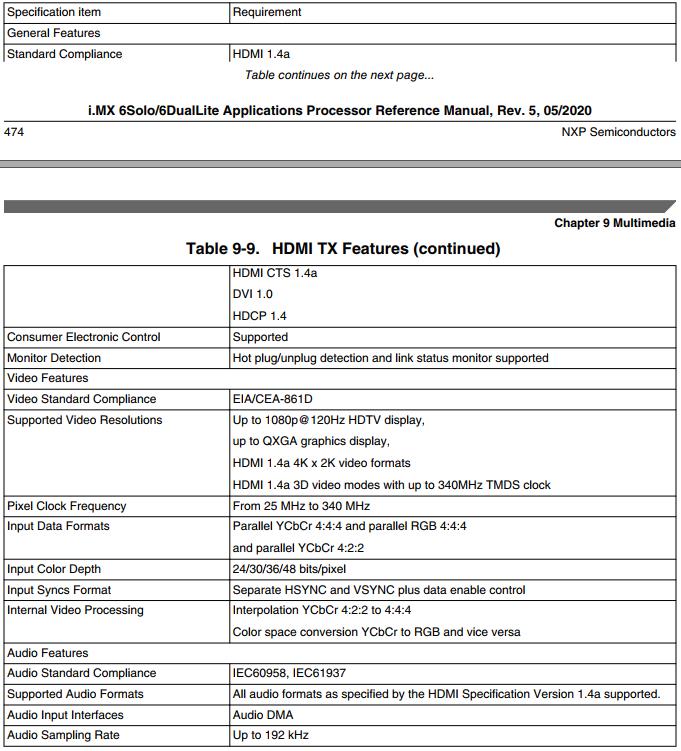

9.9 HDMI TX - 高清多媒体接口发射器

9.9.1 HDMI介绍

HDMI(高清多媒体接口)是一种紧凑的音频/视频接口,用于传输未压缩的数字视频数据和未压缩/压缩的数字音频数据。HDMI连接数字音频/视频源,如机顶盒、蓝光光盘播放机、个人电脑(pc)、视频游戏机和AV接收器到兼容的数字音频设备、计算机显示器和数字电视。

HDMI支持单一电缆上的任何电视或PC视频格式,包括标准、增强和高清视频,多达8个数字音频通道,以及消费电子控制(CEC)连接。CEC允许HDMI设备在必要时相互控制,并允许用户使用一个远程控制手持设备操作多个设备。

由于HDMI与数字视觉接口(DVI)使用的信号电兼容,因此不需要进行信号转换,使用DVI-to-HDMI适配器时,视频质量也不会下降。

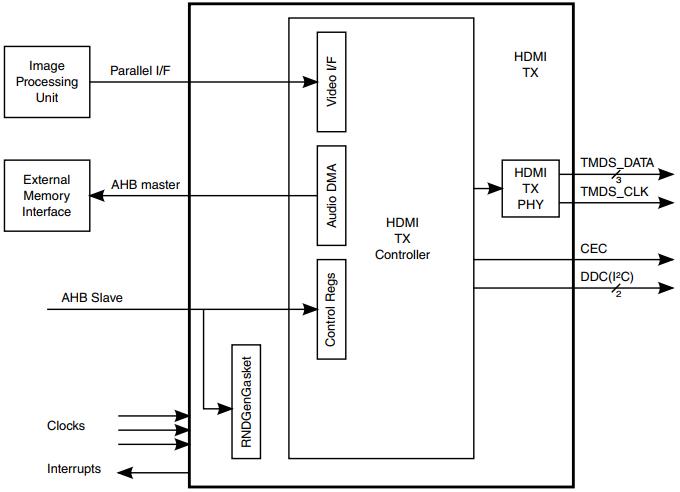

HDMI发射器(HDMI TX)由两部分组成:

HDMI TX控制器

HDMI TX物理层

下图描述了HDMI TX集成方案:

视频接口与24位/像素数据并行,并独立信号用于垂直(VSYNC)和水平(HSYNC)同步。视频数据由图像处理单元(IPU)提供。

内部音频DMA通过主AHB接口从外部存储器读取音频数据。HDMI TX是通过AHB接口控制的。

9.9.2 特性

HDMI TX特性如下表所示。

9.10 显示/传感器MIPI接口

9.10.1 介绍

IMX 6Solo/6DualLite应用处理器具有MIPI DSI/CSI-2接口,包括:

与MIPI D-PHY Tx相关联的MIPI DSI主机控制器(一个时钟通道,两个数据通道)

与MIPI D-PHY Rx相关联的MIPI CSI-2主机控制器(一个时钟通道,两个数据通道)

9.10.2 MIPI DSI

MIPI DSI是一种高性能的串行互连总线,用于连接显示系统和主机系统。

在芯片中有一个DSI端口实例。这个接口支持从80Mbps到1gbps的速度每数据通道。DSI接收器核心可以通过通道管理管理一个时钟通道和多达4个数据通道,但两个数据通道是在发射器D-PHY中实现的,因此显示端口的最大吞吐量是2Gbps。

DSI主机核心能够支持多种分辨率和格式:

• Resolution:

• QQVGA

• QCIF, QVGA

• CIF

• VGA

• WVGA

• SVGA

• XVGA

• Pixel format:

• RGB565

• LRGB565

• RGB666

• RGB888 DSI可以支持命令和视频模式,最多支持四个虚拟通道,以容纳多个显示器。

命令和视频模式支持(类型1、2、3和4显示架构)

模式切换:低功耗和超低功耗

突发模式:双视频通道

无突发模式:单视频通道

总线转变

故障错误恢复方案

DPI和DBI可以同时存在于系统中,但在某一时刻只有一个是活跃的。

9.10.3 MIPI CSI-2

MIPI CSI-2是一种高性能的串行互连总线,用于将摄像头传感器连接到主机系统。

芯片中有一个CSI-2端口实例。该接口支持从80mbps到1gbps每数据通道的速度。CSI-2接收器核心可以通过通道管理和解包处理管理一个时钟通道和多达两个数据通道,提供最大吞吐量为4gbps的传输速率。

9.10.4 D - PHY

D-PHY作为MIPI DSI和CSI-2接口的物理层。

D-PHY收发模块负责高速(HS)或低功耗(LP)模式下的数据传输和接收。高速模式用于高速数据传输,而低功耗模式用于控制目的。点对点通道互连可用于数据或时钟信号传输。高速接收机是差分线接收机,而低功率接收机是未端接的单端接收机电路。

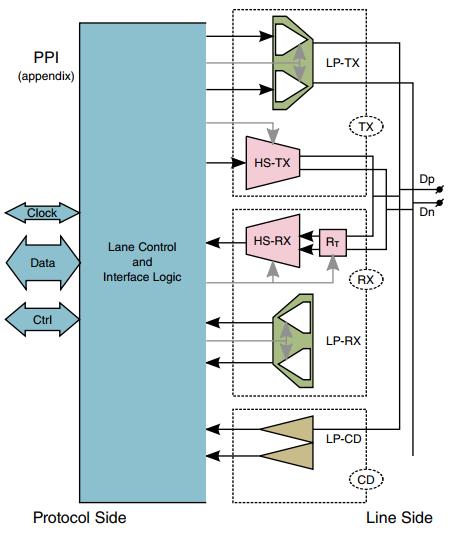

单端模块如下图所示。

有一个实例的D-PHY TX(硬宏;两个数据线,一个时钟线,PLL)和一个实例的D-PHY RX(硬宏:四个数据线,一个时钟线,没有PLL)在i.MX 6Solo/6DualLite。

9.11 音频子系统

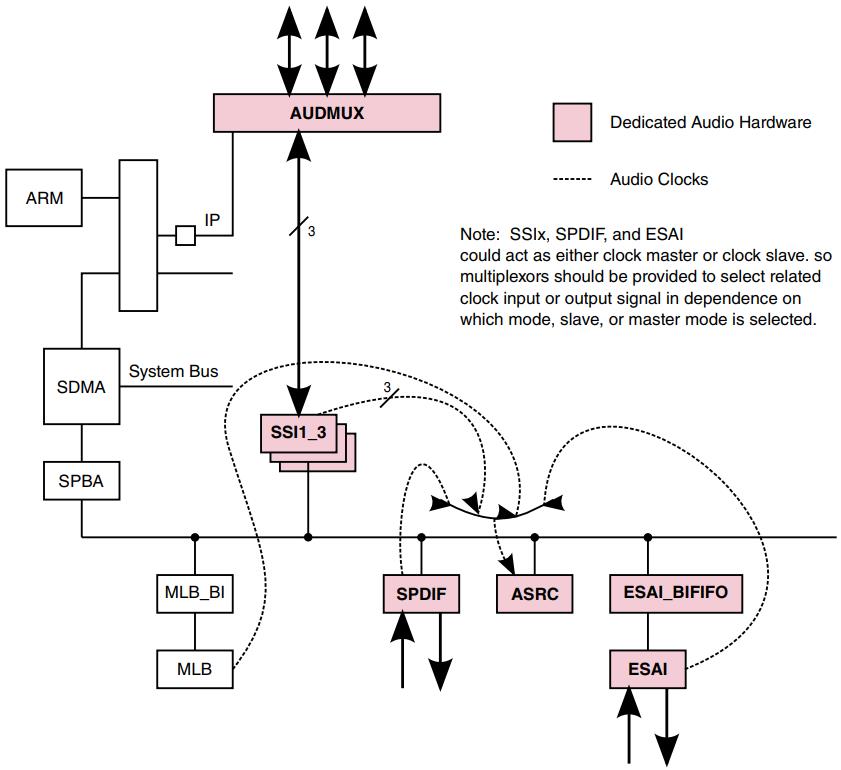

音频子系统由ssi1、ssi2、ssi3、AUDMUX、ESAI、SPDIF、ASRC、MLB等模块组成。此外,必须对IOMUX进行适当配置,以便信号在芯片中进出。

音频子系统模块概述提供了每个音频子系统组件模块的概述,然后是特定于模块的部分。

9.11.1 音频子系统模块介绍

下图显示了音频子系统的高级框图。

SSI1-3为同步串行接口,用于传输音频数据。SSI1-3在共享外围总线上。它们的串行线不是直接连接到IOMUX,而是连接到数字音频多路复用器(AUDMUX)。

AUDMUX为进出芯片外设备的串行接口(SSI1、SSI2或SSI3)提供灵活的、可编程的路由。AUDMUX路由音频数据(甚至将多个分时复用的音频流拼接在一起),但本身并不解码或处理音频数据。ARM控制AUDMUX,但AUDMUX可以在ARM处于低功耗模式时路由数据。

ESAI(增强串行音频接口)提供了一个全双工串行端口,用于与各种串行设备进行串行通信,包括工业标准编解码器、SPDIF收发器和其他处理器。ESAI由独立的发射机和接收机部分组成,每个部分都有自己的时钟发生器。ESAI连接IOMUX和ESAI_BIFIFO模块。

ESAI_BIFIFO (ESAI总线接口和FIFO)是ESAI模块和共享外设总线之间的接口。它包含用于缓冲与ESAI之间的数据的fifo。它还提供了将ESAI的24位数据总线与共享外围总线的32位数据总线匹配所必需的数据字对齐和填充。

SPDIF(索尼/飞利浦数字接口)音频模块是一个立体声收发器,允许处理器通过它接收和传输数字音频。SPDIF接收器部分包括一个频率测量块,允许精确测量传入采样频率。一个恢复的时钟由 SPDIF接收部分提供,可以用于驱动系统中的内部和外部组件。SPDIF连接到共享外围总线。

异步采样率转换器(ASRC)将与输入时钟相关联的信号的采样率转换为与不同输出时钟相关联的信号。ASRC支持多达10个通道的并发采样率转换超过120dB THD+N。每个通道的采样率转换与一对输入和输出采样率相关联。ASRC支持多达3个采样率对。ASRC连接到共享外围总线。

9.11.2 同步串行接口(SSI)

同步串行接口(SSI)是一个全双工串行端口,允许使用各种串行协议与外部设备通信。SSI支持多种协议(SSI正常协议、SSI网络协议、I2S协议和AC-97协议)、位深(最高为24位/字)和时钟/帧同步选项。

SSI有两对15x32 fifo和外部DMA控制器的硬件支持,以最小化其对系统性能的影响。第二对fifo提供了第二个音频流的硬件交错,在两个时隙同时使用的情况下减少了CPU开销。

三个ssi可以同时支持三个音频流(可能以不同的采样率)。SSI1、SSI2和SSI3位于共享外围总线上。由于SDMA可以直接访问SSI1…SSI3(位于共享外围总线上),它们可以用于高带宽数据传输,以优化总线带宽消耗。

9.11.3 数字音频 MUX (AUDMUX)

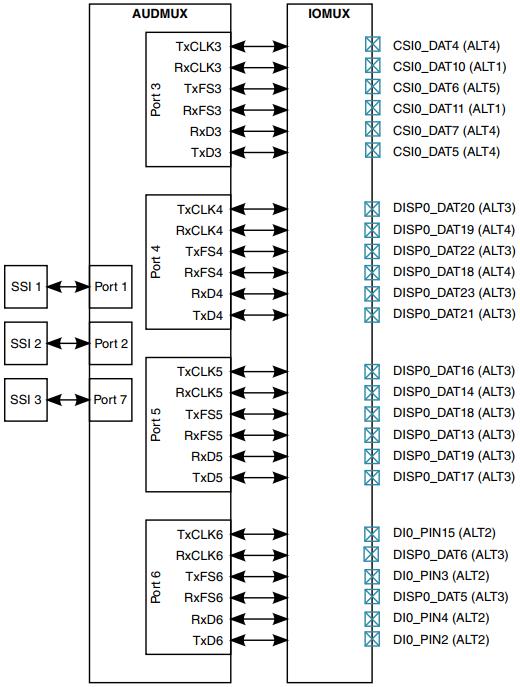

数字音频Mux (AUDMUX)提供了一种可编程互连结构,用于在主机串行接口(如SSI)和外围串行接口(即音频和语音编解码器)之间进行语音、音频和同步数据路由。

AUDMUX包括两种类型的接口。内部端口连接到处理器串行接口,外部端口连接到芯片外的音频设备。通过配置适当的主机和外围端口,可以实现所需的连接。

该AUDMUX提供了灵活的,可编程的片上串行接口与片外音频设备之间的路由。AUDMUX路由音频数据(甚至将多个分时复用的音频流拼接在一起),但本身并不解码或处理音频数据。

下图说明了AUDMUX是如何在系统中连接的。

9.11.4 增强串行音频接口(ESAI)

增强型串行音频接口(ESAI)提供了一个全双工串行端口,用于与各种串行设备进行串行通信,包括工业标准编解码器、SPDIF收发器和其他处理器。

ESAI由独立的发射机和接收机部分组成,每个部分都有自己的时钟发生器。所有串行传输同步到一个时钟。附加的同步信号被用来描绘字帧。正常的操作模式是用来以一个周期的速率(每个周期一个字)传输数据。网络模式也用于定期传输;但是,它支持每个时间段最多32个单词(时间段)。该模式可用于构建时分多路复用(TDM)网络。相反,按需模式用于非周期性的数据传输,并在数据可用时以高速串行传输数据。

ESAI有12个引脚用于与外部设备的数据和时钟连接。ESAI在内部连接到ESAI_BIFIFO,而不是直接连接到共享外围总线。ESAI接口是为24位数据总线设计的,而共享的外围数据总线是32位宽的。此外,ESAI数据路径只有双缓冲,不允许在应用程序处理器环境中提供有效的DMA服务。ESAI_BIFIFO允许增加与共享外围总线匹配的数据缓冲和数据宽度。

9.11.5 索尼/飞利浦数字接口(SPDIF)

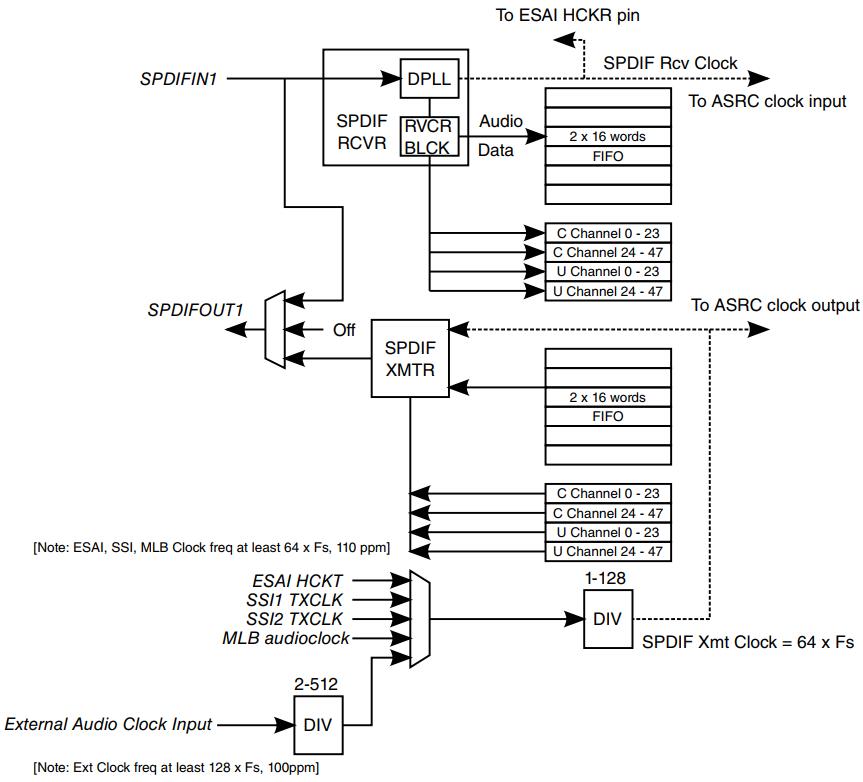

SPDIF模块是一种立体声,允许处理器使用IEC60958标准消费者格式通过它传输数字音频。该芯片提供一个具有一个输出的SPDIF发射器。

SPDIF允许处理SPDIF通道状态(CS)和用户(U)数据。

对于SPDIF发射器,音频数据由处理器通过SPDIFTxLeft和SPDIFTxRight寄存器提供,数据存储在两个16个字深的fifo中,一个用于右通道,另一个用于左通道。FIFO支持可编程水印级别,因此当两个FIFO中的空数据字位置的组合数量为8、16、24或32个字时,可以触发FIFO空服务请求。建议对水印级别进行编程,以在16个字位置为空时触发FIFO空服务请求。为了在处理FIFO Empty服务请求时获得最佳性能,应该交替地编写FIFO,从左通道FIFO开始。通道状态位也通过相应的寄存器提供。SPDIF发射器生成双相标记格式(IEC 60958)的SPDIF输出bit流,由音频数据、通道状态和用户位组成。

SPDIF模块处理的数据是24位宽的。24位SPDIF数据在32位共享外围总线数据字的24位最低有效位中对齐。当从外围总线的传输fifo中存储数据时,SPDIF Transmitter忽略32位字的8个最重要的位。当数据从接收fifo读取到外围总线时,32位字的8个最重要的位被SPDIF Receiver模块置零。

注意,16位数据在SPDIF的24位字格式中是左对齐的。16位数据传输时,32位的字写到SPDIF传输fifo应该创建如下:16位数据应该位于中间的两个字节的8位32位数据字和LSB必须设置为零,而MSB的8位将被忽略。

SPDIF Transmit时钟由SPDIF内部时钟产生模块产生,时钟源来自SPDIF块外部。ESAI、SSI和MLB时钟源应提供至少64 x Fs的时钟,其中Fs是采样频率。外部时钟源应至少提供128 × Fs。只要乘因子是2的幂(例如128x、256x或512x),就可以提供更高频率的时钟。此外,时钟频率精度应提供100ppm或更好。SPDIF收发器时钟图如下:

9.11.6 异步采样率转换器(ASRC)

输入的音频数据可以以不同的采样率从不同的源接收。传出的音频数据可能有不同的采样率,它也可以与输出时钟相关联,而输出时钟与输入时钟是异步的。

ASRC将与输入时钟相关联的信号的采样率转换为与不同输出时钟相关联的信号。ASRC支持多达10个通道的并发采样率转换约-120dB THD+N。每个通道的采样率转换与一对输入和输出采样率相关联。ASRC支持多达3个采样率对。

在实时音频用例中,两个输入/输出采样率时钟都被激活。两个采样速率时钟都直接与ASRC连接,ASRC硬件采用输入时钟与输出时钟的比值估计来实现采样速率转换。

SSI1, SSI2, SSI3, S/PDIF, ESAI和MLB音频模块可以作为时钟主或时钟从。如图9-14和表9-13所示,在芯片水平上提供多路复用器,根据模块的工作模式选择模块的时钟信号(输入或输出)连接到ASRC输入端。图9-14展示了用于所有ASRC输入时钟的多路复用单元。表9-13给出了每个ASRC输入时钟的详细时钟、多路复用控制和数据位。直连ASRC的音频块时钟(不采用多路复用方案)请参见表9-14。

在非实时流音频用例中,不需要提供输入采样率时钟。相反,在ASRC接口寄存器中设置理想比率值转换。在这种情况下,必须只提供输出采样率时钟,并使用寄存器中输入与输出的固定比率来执行采样率转换。

以上是关于Multimedia的主要内容,如果未能解决你的问题,请参考以下文章