CMOS反相器

Posted 硬件老钢丝

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了CMOS反相器相关的知识,希望对你有一定的参考价值。

一、COMS反相器的工作原理

我们利用Cadence软件对反相器进行仿真,其基本结构如下:上面是一个PMOS,下面是一个NMOS。

为了保证电路能够正常工作,电源电压VDD大于两个管子的开启电压的绝对值之和,即VDD》VTH_n+|VTH_p|。

下图为一个CMOS反相器的基本分析,对于一个输入U1为高电平时,NMOS导通,PMOS截止,因此 此时的 输出U0由于NMOS导通的关系,呈现GND电位,也就是低电平;当输入U1为低电平时,NMOS截止,PMOS导通,U0的电位与VDD一致。因为整体来看,不管V1呈现高电位还是低电位,出来的总是反相的电位。(我们这里一般都是说的稳定高电平和稳定低电平的时候,电流几乎为0)

为了更好地分析电路的工作状态,我们进行如下的分析。

1、U1输入为0时,N管截止,P管导通,从而导致整个上下通路是断路,所以ID=0,U0=VDD;

2、U1输入增大到VTn时,N管导通,并且P管也是导通的;

3、U1输入在VTn到VDD/2之间时,N管由于是从截止变化,所以他的等效阻抗开始减小,P管开始像截止区迈进,进而等效阻抗开始变大;

4、U1=VDD/2时,RN+RP等效阻抗是最小的,也就是说明这个ID应该是最大大的;

5、U1输入在VDD/2到VDD-|VTp|之间时,N管等效阻抗越来越小,P管逐渐趋于截止,整体的UO趋于低电位;

6、U1输入为VDD-|VTp|时.P管临界截止

7、U1输入到VDD-|VTp|到VDD之间,N管导通,P管截止,直到VDD,此时U0的输出呈现GND电位。

下图整好展现了这种现象。(这里是数字电路里面的分析,用高低电平来分析的,模拟分析是类似的。)

模拟里面的分析可以用下图所示

二、仿真验证

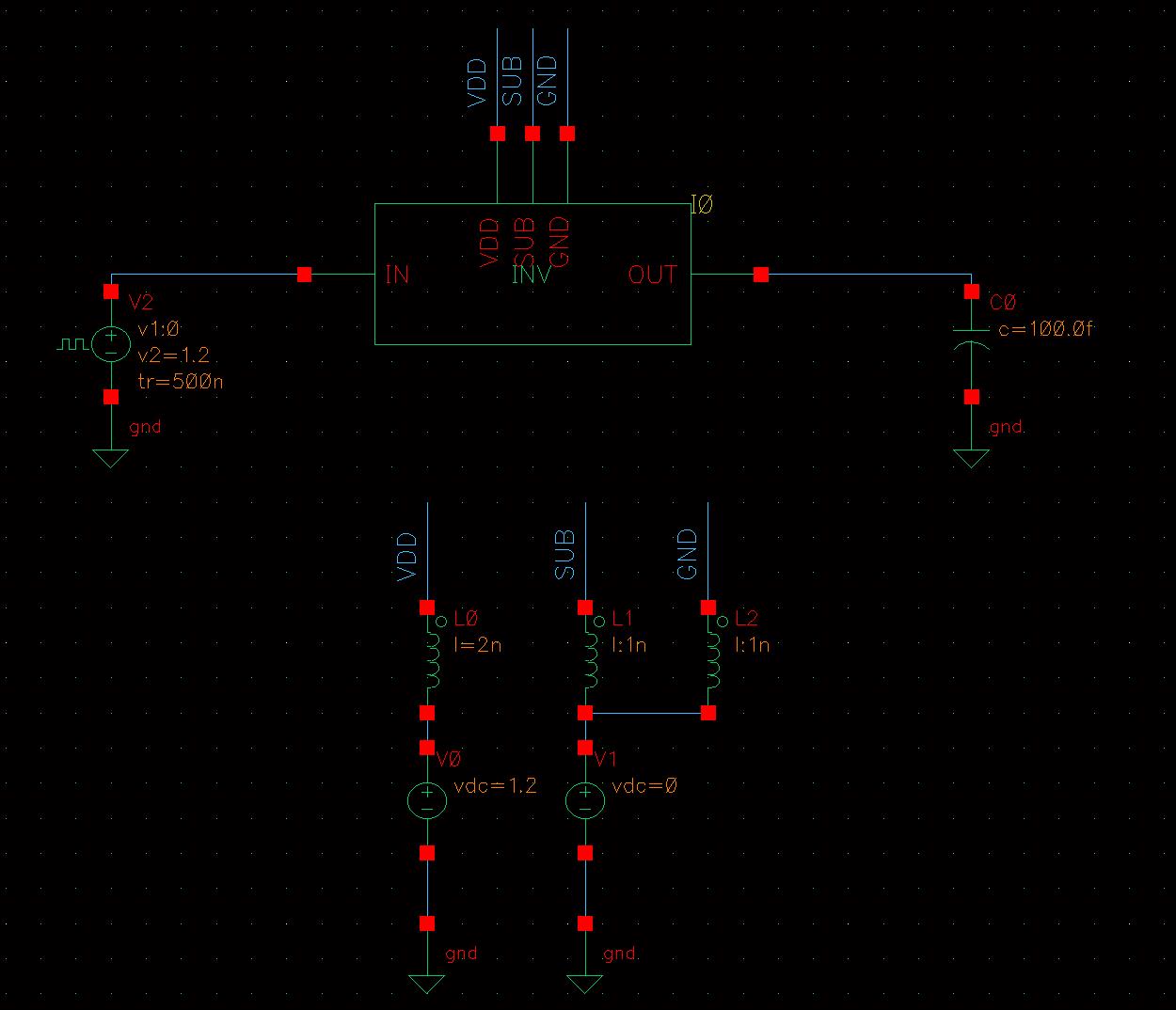

我们搭建了下图所示的电路(chris讲的)

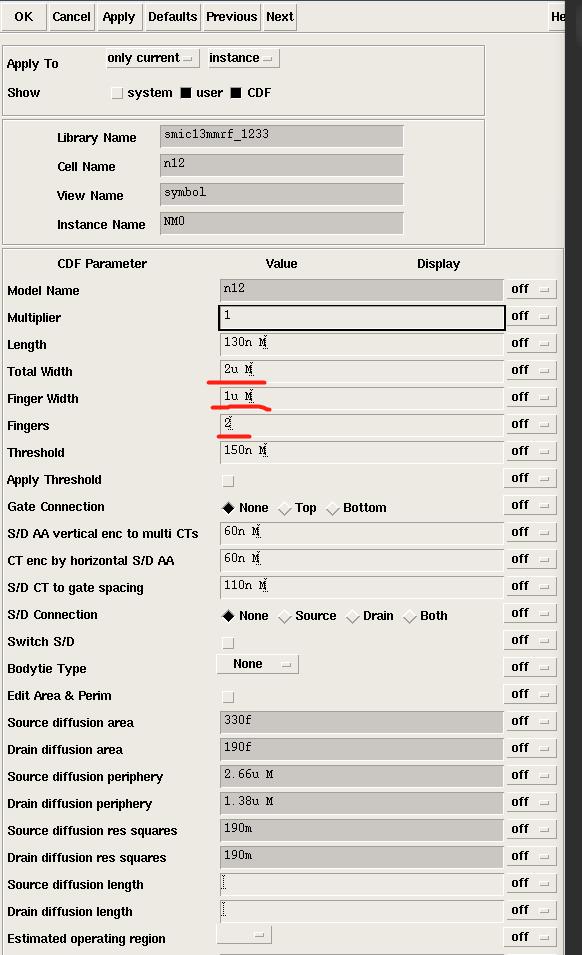

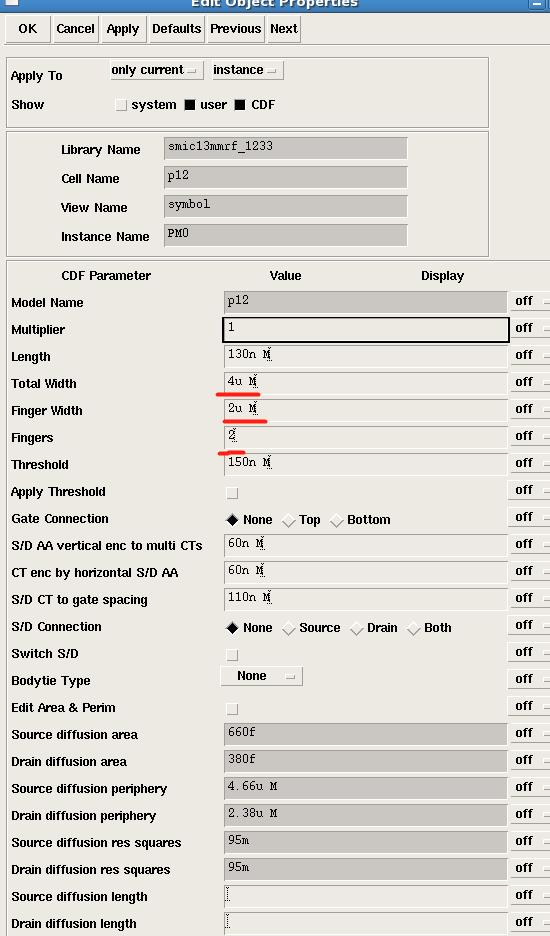

考虑到N管和P管的电子迁移率问题,这里设置P管得栅宽W为N管栅宽的二倍,保持L一致,从而保证电流基本一致。

然后搭建仿真电路,数据都可以看Chris的视频去设置。

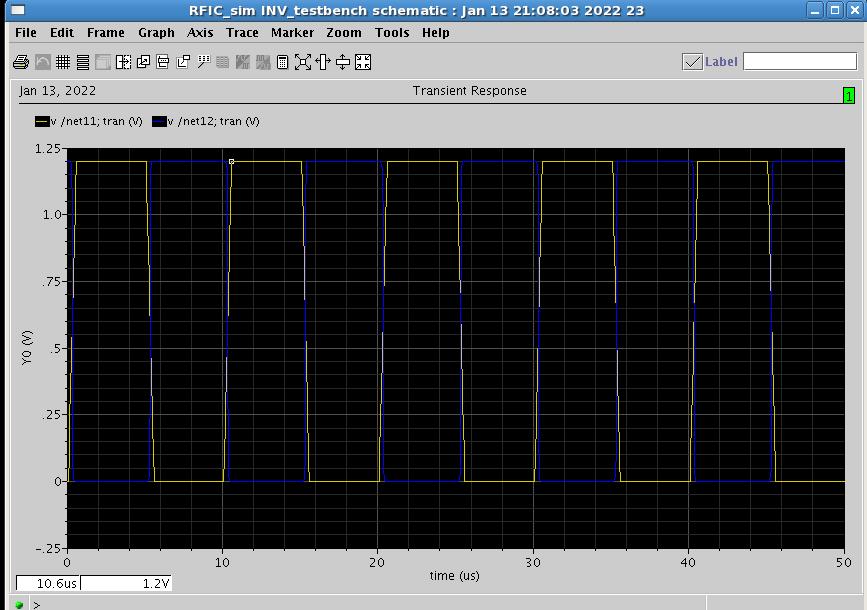

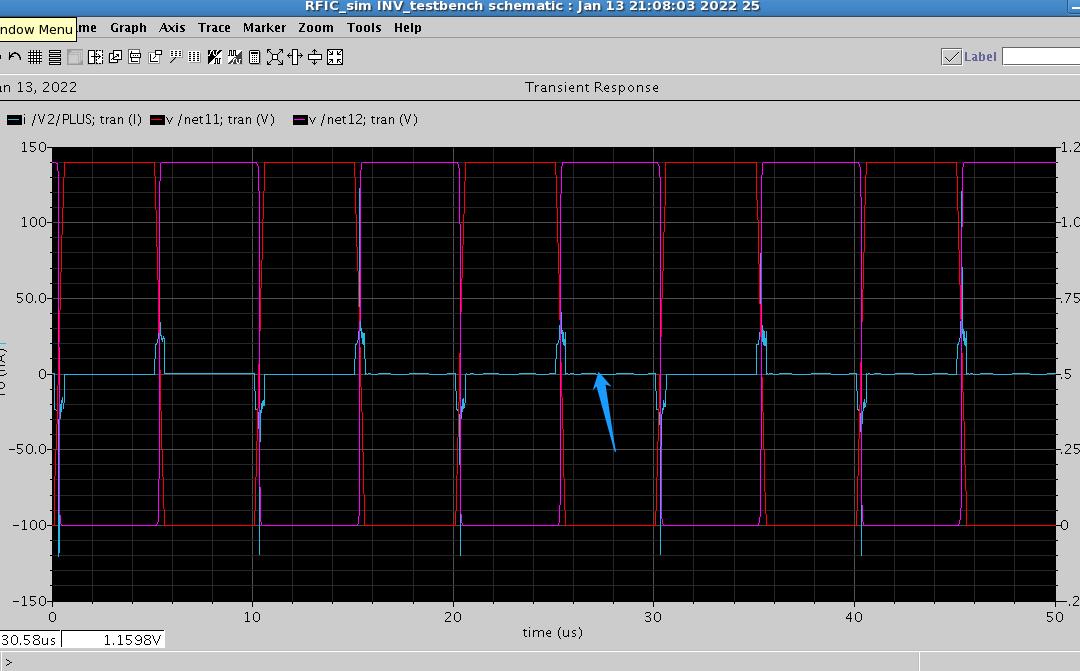

我们采用矩形输入波形,占空比为50%的波形。

可以看到输入输出电压呈现反相。

顺便看一下电流波形,可以看出电流的最大值出现在翻转的中心处。完美的验证了我们的理论。

以上是关于CMOS反相器的主要内容,如果未能解决你的问题,请参考以下文章