使用FPGA点亮LED的多种方法讲解

Posted 恒星QRS

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了使用FPGA点亮LED的多种方法讲解相关的知识,希望对你有一定的参考价值。

FPGA点亮LED的多种操作方法

LED的硬件链接

对于嵌入式而言,要想实现预计的功能就必须了解硬件上的连接,在这里使用的是alter的EP4CE10F17C8这款芯片,其LED连接情况如下。

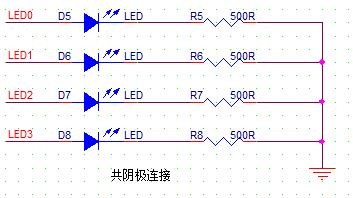

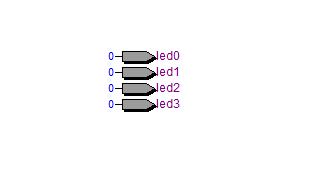

上图为LED与FPGA芯片的连接方式

上图为LED的连接方式,在图中可以看出,LED的正极都连到了同一个3.3V上,这种连接方式称为共阳极连接。相反的就存在共阴极连接,如下图:

在这里我们主要分析共阳极连接,由于所有的LED正极都连接着3.3V的电源,所以我们只需要给LED的负极接入一个低电平,那LED就可以点亮,所以需要点亮的LED芯片管脚需要输出低电平。同理可得:共阴极连接需要在芯片管脚输出高电平。在了解了硬件连接后,我们开始编写代码。

点亮代码

方法一:

module led(

output led0, //定义第一个LED灯

output led1, //定义第二个LED灯

output led2, //定义第三个LED灯

output led3 //定义第四个LED灯

);

assign led0 = 0; //将第一个LED灯所连接到的芯片引脚置于低电平

assign led1 = 0; //将第二个LED灯所连接到的芯片引脚置于低电平

assign led2 = 0; //将第三个LED灯所连接到的芯片引脚置于低电平

assign led3 = 0; //将第四个LED灯所连接到的芯片引脚置于低电平

endmodule

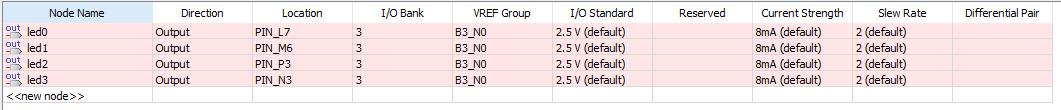

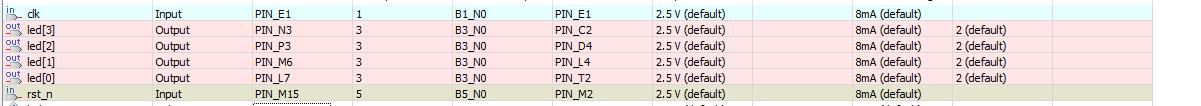

在这里定义LED0-3的输出电压全部都为低电平,特别提示,在代码中二进制的0代表低电平,通常位0V;1代表为高电平,通常为3.3V。代码经过编译后我们进行管脚锁定。

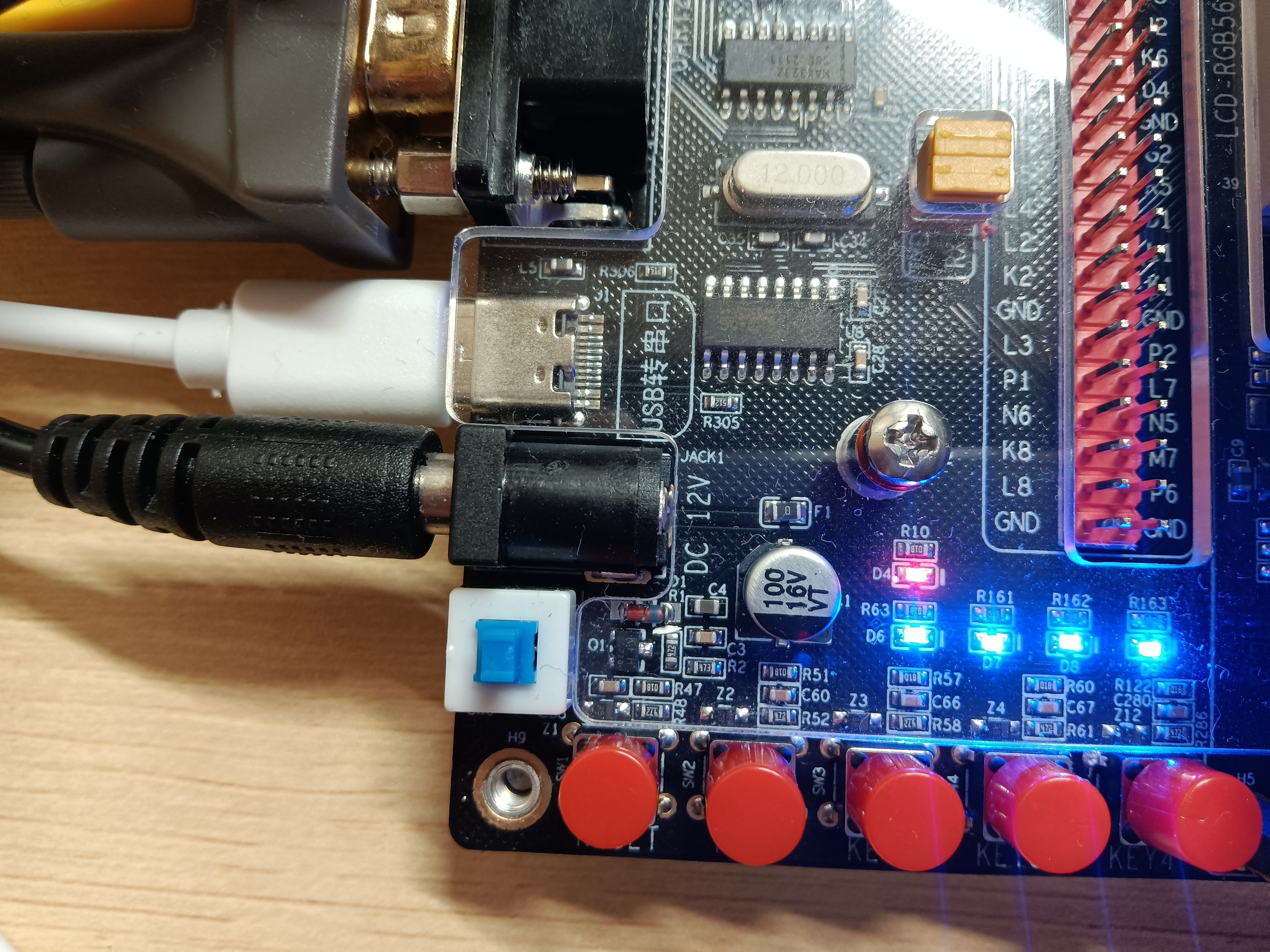

管脚如我们在上面提到的一样去分配;接下来我们去烧录,我们就可以得到结果

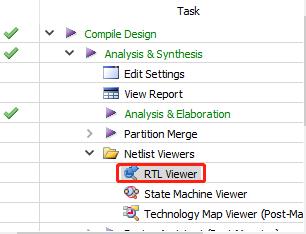

在讲第二种编写方式前,我们先查看一下这种编写方式的RTL,打开方式如下:

我们打开后查看RTL图发现,这种方式的编写没有任何寄存器,而是将输入直接给到了输出。

方法二

module led(

input wire clk, //定义一个时钟,一般情况下为50MHz

input wire rst_n, //复位信号,高电平有效

output reg led0, //定义第一个LED灯

output reg led1, //定义第二个LED灯

output reg led2, //定义第三个LED灯

output reg led3 //定义第四个LED灯

);

always@(posedge clk or negedge rst_n) //定义一个触发器,posedge clk表示clk为上升沿触发,negedge rst_n表示rst_n为下降沿触发

if(!rst_n)begin //高电平复位

led0 <= 1; //初始化LED管脚输出

led1 <= 1; //初始化LED管脚输出

led2 <= 1; //初始化LED管脚输出

led3 <= 1; //初始化LED管脚输出

end

else begin

led0 <= 0; //LED管脚输出置0,输出高电平,点亮LED

led1 <= 0; //LED管脚输出置0,输出高电平,点亮LED

led2 <= 0; //LED管脚输出置0,输出高电平,点亮LED

led3 <= 0; //LED管脚输出置0,输出高电平,点亮LED

end

endmodule

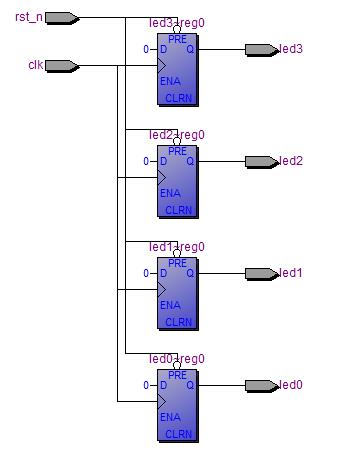

同样的在编译后分配引脚上板后任然可以点亮,查看RTL图,RTL将会变为下图所示

在图中,我们发现,每一个LED的信号在输出的前面都多加了一个触发器,在模电中,第一种方法产生的电路叫做逻辑电路,不受时间的影响,第二种的叫做时序电路,它有严格的时序要求,在FPGA的后续研究中,多数都是以时序逻辑去分析的,所以这里必须掌握的很好。

方法三

module led(

input wire clk,

input wire rst_n,

output reg[3:0] led

);

always@(posedge clk or negedge rst_n)

if(!rst_n)

led <= 4'b1111;

else

led <= 4'b0000;

endmodule

在进行管脚分配时需要特别注意下,此时的变量变为了led[0]…,在这里我们只需要将他理解为四个led中的第一个既可以。

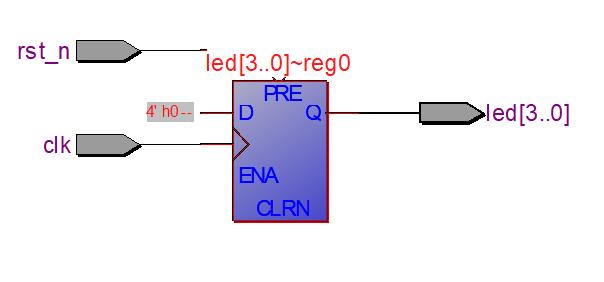

验证上板后任然是可以点亮的,这时我们在查看RTL图

多个触发器变为了一个,这样可以大大的减少逻辑资源。而且这类方法在后面的流水灯中也有着较大的作用,可以大大较少流水灯的代码冗余度。

总结

到这就大致讲完了LED的点亮,如有问题,还请指出,代码复制后不能达到预计效果,也可以联系我,我将尽我所能的帮助你。

以上是关于使用FPGA点亮LED的多种方法讲解的主要内容,如果未能解决你的问题,请参考以下文章

iCore3 双核心板_FPGA例程二:GPIO输出实验——点亮三色LED

史上最全的LED点灯程序—使用STM32FPGALinux点亮你的LED灯