VIVADO除法IP注意事项

Posted 朽月

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了VIVADO除法IP注意事项相关的知识,希望对你有一定的参考价值。

VIVADO除法IP注意事项

参考文献

[1]、V3学院——软件无线电课程

项目简述

这篇博客主要记录VIVADO中除法IP的注意事项,遇见一些新的知识点应该做相应的笔记。

本次实验所用的软硬件环境如下:

[1]、VIVADO 2019.2

[2]、Modelsim 10.7

注意事项

第一个注意事项

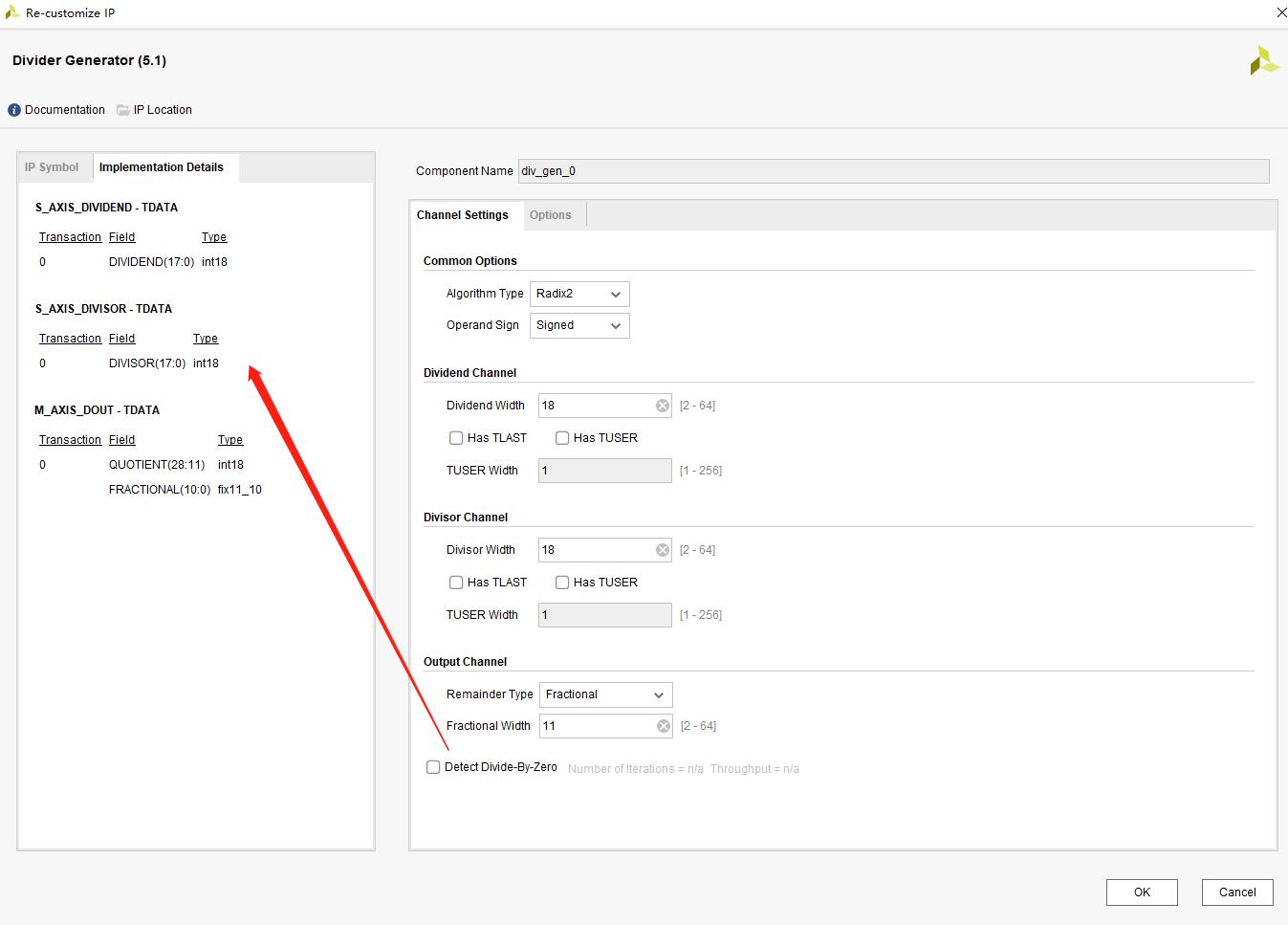

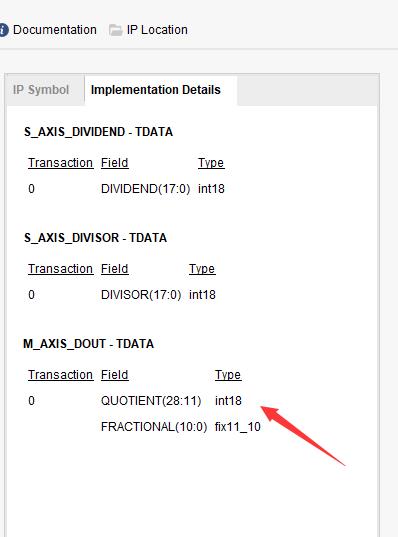

首先可以在除法IP的定制界面看到被除数、除数、商的位宽有详细的说明:

从上面的位宽信息,我们可以发现被除数有18位整数,除数有18位整数,商有18位整数、11位小数。当然这里的被除数与除数可以是量化完之后的结果,但是量化要注意被除数与除数乘以相同的数。

第二个注意事项

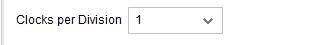

除法器的下面的选项是控制除法器每隔多少个时钟有一个有效的输出:

第三个注意事项

这两种模式的解释如下:

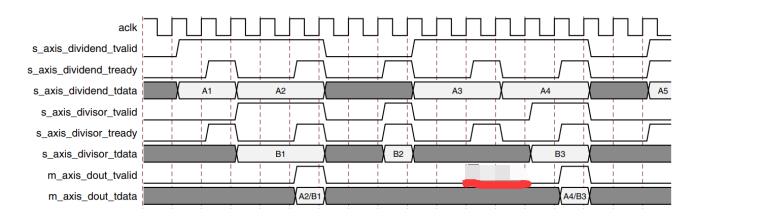

Non Blocking 非阻塞模式

非阻塞模式就是送入除数和被除数接口当除数和被除数的 TREADY 和 TVALID的都共同有效时刻的 TDATA 数据被除法器接收并运算, 如果单个除数或者被除数 TREADY 和 TVALID 一起有效, 不会被除法器接收数据运算。

有些特殊场景希望使用资源少,也可以使用 H Radix + Non Blocking 注意除数是否有效, 除数如果无效还不能取其计算的结果。

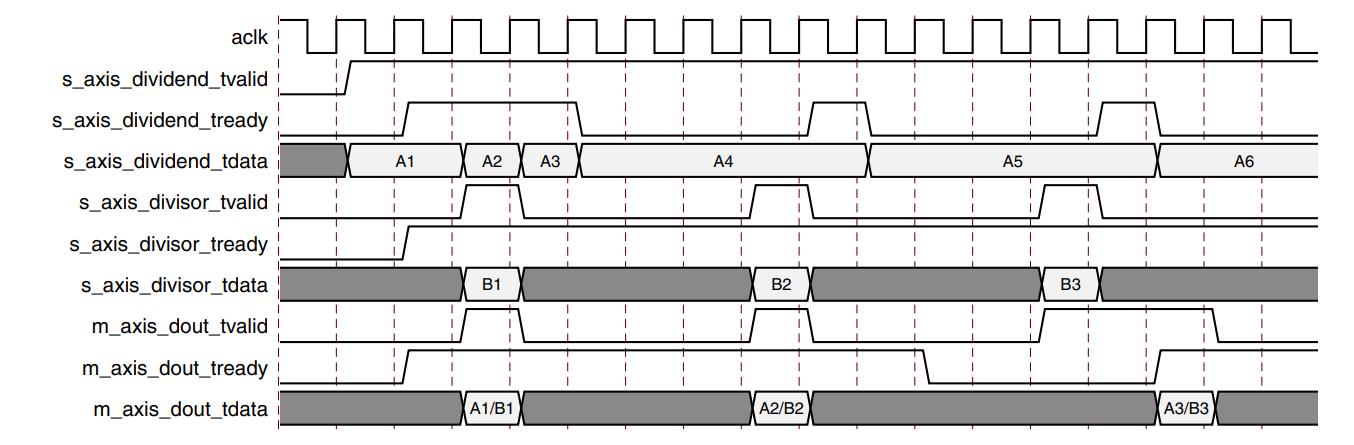

Blocking 阻塞模式

阻塞模式相当于在除数和被除数端口上都增加了 fifo, 除数和被除数不要求TVALID 和 TREADY 都同时有效, 可以分拍有效, 这时候除法器还会根据送入除法器的接口数据顺序进行计算。 如下图时序

除数和被除数数据来临的时刻不相等, 而希望按照顺序进行做运算, 这时候使用 blocking 模式最好。

第四个注意事项

对于有符号数的除法,IP输出的数据不能直接供下一级使用,于是进行相应的处理。 这里主要是因为输出的结果小数位有一个单独的符号位,我们需要把这个符号位去掉再拼接,例如对于下面的例子:

输出数据小数位的第11位是符号位,进行拼接的代码如下:

assign data = M_AXIS_DOUT_tdata[28:11],M_AXIS_DOUT_tdata[10:0];

总结

上面的是一些关于VIVADO除法IP的注意事项,认为文章有帮助的同学们可以关注、点赞、转发支持。

以上是关于VIVADO除法IP注意事项的主要内容,如果未能解决你的问题,请参考以下文章