adreno源码系列dts配置与gpu列表

Posted bubbleben

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了adreno源码系列dts配置与gpu列表相关的知识,希望对你有一定的参考价值。

以Find x3 pro设备树文件为例进行分析:https://github.com/oppo-source/android_kernel_modules_and_devicetree_oppo_sm8350/blob/oppo/sm8350_s_12.1_find_x3_pro/vendor/qcom/proprietary/devicetree/qcom/sm8150-gpu.dtsi

1. dts配置文件

#define MHZ_TO_KBPS(mhz, w) ((mhz * 1000000 * w) / (1024))

&soc

pil_gpu: qcom,kgsl-hyp

compatible = "qcom,pil-tz-generic";

qcom,pas-id = <13>;

qcom,firmware-name = "a640_zap";

memory-region = <&pil_gpu_mem>;

;

// kgsl配置

msm_gpu: qcom,kgsl-3d0@2c00000

label = "kgsl-3d0";

compatible = "qcom,kgsl-3d0", "qcom,kgsl-3d";

status = "ok";

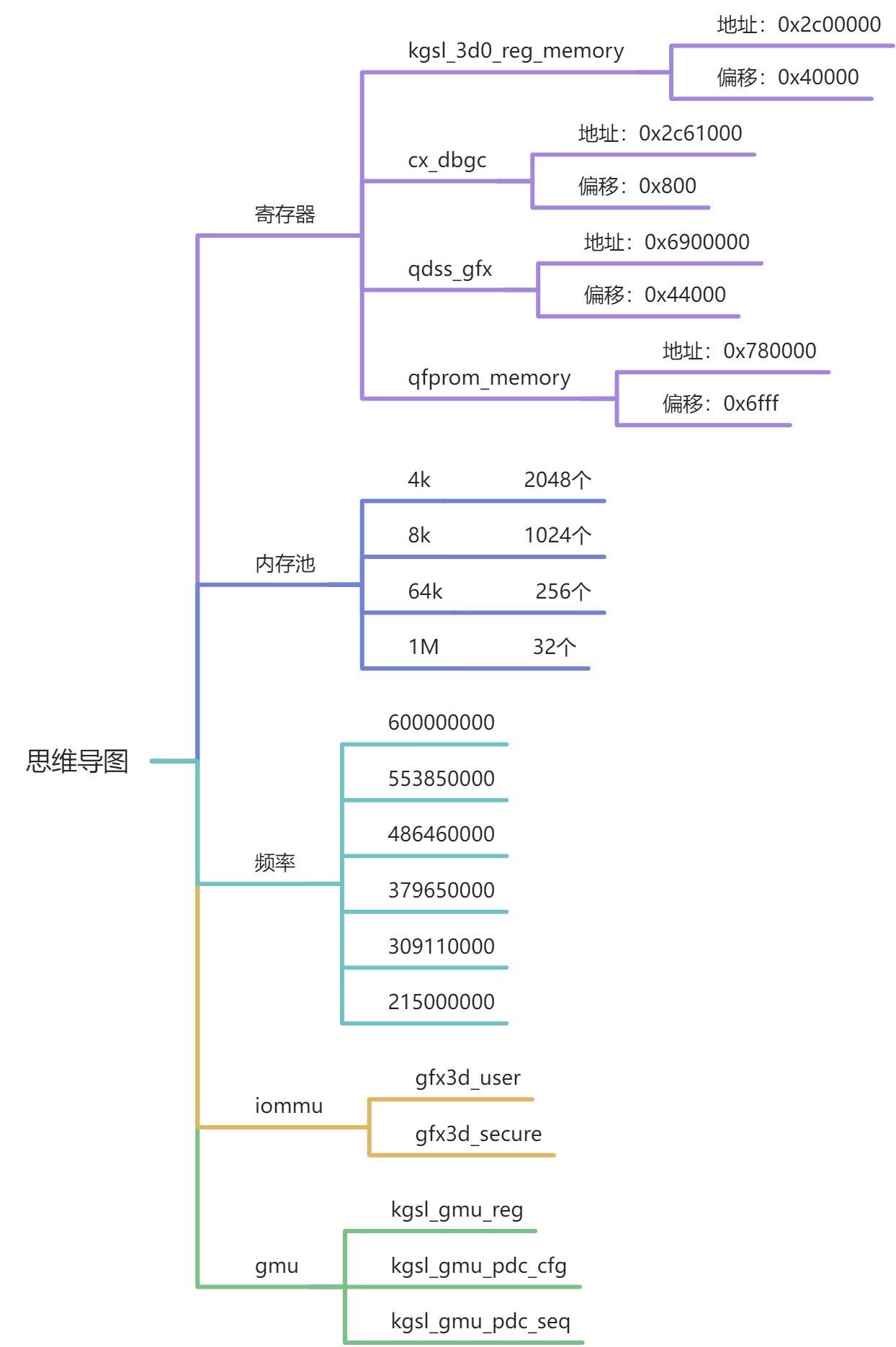

// 寄存器地址与偏移量

reg = <0x2c00000 0x40000>, <0x2c61000 0x800>,

<0x6900000 0x44000>, <0x780000 0x6fff>;

// 寄存器名称

reg-names = "kgsl_3d0_reg_memory", "cx_dbgc",

"qdss_gfx", "qfprom_memory";

interrupts = <0 300 IRQ_TYPE_LEVEL_HIGH>;

// 中断名称

interrupt-names = "kgsl_3d0_irq";

qcom,id = <0>;

// 主版本号:6

// 副版本号:4

// patchid: 0

qcom,chipid = <0x06040000>;

// 默认频率

qcom,initial-pwrlevel = <5>;

qcom,gpu-quirk-secvid-set-once;

qcom,gpu-quirk-cx-gdsc;

qcom,idle-timeout = <80>; //msecs

qcom,no-nap;

qcom,highest-bank-bit = <15>;

qcom,min-access-length = <32>;

qcom,ubwc-mode = <3>;

qcom,gpu-qdss-stm = <0x161c0000 0x40000>; // base addr, size

#cooling-cells = <2>;

// 时钟

clocks = <&gcc GCC_GPU_CFG_AHB_CLK>,

<&gpucc GPU_CC_CXO_CLK>,

<&gcc GCC_DDRSS_GPU_AXI_CLK>,

<&gcc GCC_GPU_MEMNOC_GFX_CLK>,

<&gpucc GPU_CC_CX_GMU_CLK>,

<&gpucc GPU_CC_AHB_CLK>;

// 时钟名称

clock-names = "gcc_gpu_ahb", "rbbmtimer_clk",

"gcc_gpu_axi_clk", "gcc_gpu_memnoc_gfx",

"gmu_clk", "gpu_cc_ahb";

qcom,isense-clk-on-level = <1>;

interconnects = <&gem_noc MASTER_GFX3D &mc_virt SLAVE_EBI1>;

interconnect-names = "gpu_icc_path";

qcom,bus-table-ddr =

<MHZ_TO_KBPS(0, 4)>, /* index=0 */

<MHZ_TO_KBPS(100, 4)>, /* index=1 */

<MHZ_TO_KBPS(150, 4)>, /* index=2 */

<MHZ_TO_KBPS(200, 4)>, /* index=3 */

<MHZ_TO_KBPS(300, 4)>, /* index=4 */

<MHZ_TO_KBPS(412, 4)>, /* index=5 */

<MHZ_TO_KBPS(547, 4)>, /* index=6 */

<MHZ_TO_KBPS(681, 4)>, /* index=7 */

<MHZ_TO_KBPS(768, 4)>, /* index=8 */

<MHZ_TO_KBPS(1017, 4)>, /* index=9 */

<MHZ_TO_KBPS(1296, 4)>, /* index=10 */

<MHZ_TO_KBPS(1555, 4)>, /* index=11 */

<MHZ_TO_KBPS(1804, 4)>; /* index=12 */

qcom,bus-table-cnoc =

<0>, /* Off */

<100>; /* On */

/* GDSC regulator names */

regulator-names = "vddcx", "vdd";

/* GDSC oxili regulators */

vddcx-supply = <&gpu_cx_gdsc>;

vdd-supply = <&gpu_gx_gdsc>;

qcom,l3-pwrlevels

#address-cells = <1>;

#size-cells = <0>;

compatible = "qcom,l3-pwrlevels";

qcom,l3-pwrlevel@0

reg = <0>;

qcom,l3-freq = <0>;

;

qcom,l3-pwrlevel@1

reg = <1>;

qcom,l3-freq = <864000000>;

;

qcom,l3-pwrlevel@2

reg = <2>;

qcom,l3-freq = <1344000000>;

;

;

/* GPU Mempools */

// kgsl内存池配置

qcom,gpu-mempools

#address-cells = <1>;

#size-cells = <0>;

compatible = "qcom,gpu-mempools";

/* 4K Page Pool configuration */

qcom,gpu-mempool@0

reg = <0>;

qcom,mempool-page-size = <4096>;

qcom,mempool-reserved = <2048>;

qcom,mempool-allocate;

;

/* 8K Page Pool configuration */

qcom,gpu-mempool@1

reg = <1>;

qcom,mempool-page-size = <8192>;

qcom,mempool-reserved = <1024>;

qcom,mempool-allocate;

;

/* 64K Page Pool configuration */

qcom,gpu-mempool@2

reg = <2>;

qcom,mempool-page-size = <65536>;

qcom,mempool-reserved = <256>;

;

/* 1M Page Pool configuration */

qcom,gpu-mempool@3

reg = <3>;

qcom,mempool-page-size = <1048576>;

qcom,mempool-reserved = <32>;

;

;

/* Power levels */

// kgsl频率配置

qcom,gpu-pwrlevels

#address-cells = <1>;

#size-cells = <0>;

compatible = "qcom,gpu-pwrlevels";

qcom,gpu-pwrlevel@0

reg = <0>;

qcom,gpu-freq = <600000000>;

qcom,level = <RPMH_REGULATOR_LEVEL_TURBO>;

qcom,bus-freq = <12>;

qcom,bus-min = <10>;

qcom,bus-max = <12>;

;

qcom,gpu-pwrlevel@1

reg = <1>;

qcom,gpu-freq = <553850000>;

qcom,level = <RPMH_REGULATOR_LEVEL_NOM_L1>;

qcom,bus-freq = <10>;

qcom,bus-min = <9>;

qcom,bus-max = <11>;

;

qcom,gpu-pwrlevel@2

reg = <2>;

qcom,gpu-freq = <486460000>;

qcom,level = <RPMH_REGULATOR_LEVEL_NOM>;

qcom,bus-freq = <9>;

qcom,bus-min = <8>;

qcom,bus-max = <10>;

;

qcom,gpu-pwrlevel@3

reg = <3>;

qcom,gpu-freq = <379650000>;

qcom,level = <RPMH_REGULATOR_LEVEL_SVS_L1>;

qcom,bus-freq = <8>;

qcom,bus-min = <7>;

qcom,bus-max = <9>;

;

qcom,gpu-pwrlevel@4

reg = <4>;

qcom,gpu-freq = <309110000>;

qcom,level = <RPMH_REGULATOR_LEVEL_SVS>;

qcom,bus-freq = <5>;

qcom,bus-min = <5>;

qcom,bus-max = <7>;

;

qcom,gpu-pwrlevel@5

reg = <5>;

qcom,gpu-freq = <215000000>;

qcom,level = <RPMH_REGULATOR_LEVEL_LOW_SVS>;

qcom,bus-freq = <4>;

qcom,bus-min = <3>;

qcom,bus-max = <5>;

;

qcom,gpu-pwrlevel@6

reg = <6>;

qcom,gpu-freq = <0>;

qcom,level = <RPMH_REGULATOR_LEVEL_RETENTION>;

qcom,bus-freq = <0>;

qcom,bus-min = <0>;

qcom,bus-max = <0>;

;

;

;

// iommu配置

kgsl_msm_iommu: qcom,kgsl-iommu@2ca0000

compatible = "qcom,kgsl-smmu-v2";

reg = <0x2ca0000 0x10000>;

gfx3d_user: gfx3d_user

compatible = "qcom,smmu-kgsl-cb";

label = "gfx3d_user";

iommus = <&kgsl_smmu 0x0 0x401>;

qcom,iommu-dma = "disabled";

;

gfx3d_secure: gfx3d_secure

compatible = "qcom,smmu-kgsl-cb";

label = "gfx3d_secure";

iommus = <&kgsl_smmu 0x2 0x400>;

qcom,iommu-dma = "disabled";

;

;

// gmu配置

gmu: qcom,gmu@2c6a000

compatible = "qcom,gpu-gmu";

reg = <0x2c6a000 0x30000>,

<0xb280000 0x10000>,

<0xb480000 0x10000>;

reg-names = "kgsl_gmu_reg",

"kgsl_gmu_pdc_cfg",

"kgsl_gmu_pdc_seq";

interrupts = <0 304 IRQ_TYPE_LEVEL_HIGH>,

<0 305 IRQ_TYPE_LEVEL_HIGH>;

interrupt-names = "kgsl_hfi_irq", "kgsl_gmu_irq";

regulator-names = "vddcx", "vdd";

iommus = <&kgsl_smmu 0x5 0x400>;

qcom,iommu-dma = "disabled";

vddcx-supply = <&gpu_cx_gdsc>;

vdd-supply = <&gpu_gx_gdsc>;

clocks = <&gpucc GPU_CC_CX_GMU_CLK>,

<&gpucc GPU_CC_CXO_CLK>,

<&gcc GCC_DDRSS_GPU_AXI_CLK>,

<&gcc GCC_GPU_MEMNOC_GFX_CLK>,

<&gpucc GPU_CC_AHB_CLK>;

clock-names = "gmu_clk", "cxo_clk", "axi_clk",

"gcc_gpu_memnoc_gfx_clk", "gpu_cc_ahb";

/* AOP mailbox for sending ACD enable and disable messages */

mboxes = <&qmp_aop 0>;

mbox-names = "aop";

;

;

2. adreno_gpu_core

/**

* struct adreno_gpu_core - A specific GPU core definition

*/

// 定义adreno gpu的核心实现

struct adreno_gpu_core

enum adreno_gpurev gpurev;

// 核心系列, 主版本号, 副版本号, patchid

unsigned int core, major, minor, patchid;

/**

* @compatible: If specified, use the compatible string to match the

* device

*/

const char *compatible;

// 支持的特性

unsigned long features;

// Pointer to the GPU family specific functions for this core[见2.1节]

const struct adreno_gpudev *gpudev;

// 性能计数器[见2.2节]

const struct adreno_perfcounters *perfcounters;

size_t gmem_size;

u32 bus_width;

/** @snapshot_size: Size of the static snapshot region in bytes */

u32 snapshot_size;

;

2.1 adreno_gpudev

struct adreno_gpudev

/*

* These registers are in a different location on different devices,

* so define them in the structure and use them as variables.

*/

// 寄存器偏移地址

unsigned int *const reg_offsets;

const struct adreno_ft_perf_counters *ft_perf_counters;

unsigned int ft_perf_counters_count;

struct adreno_coresight *coresight[2];

/* GPU specific function hooks */

int (*probe)(struct platform_device *pdev, u32 chipid,

const struct adreno_gpu_core *gpucore);

void (*snapshot)(struct adreno_device *adreno_dev,

struct kgsl_snapshot *snapshot);

irqreturn_t (*irq_handler)(struct adreno_device *adreno_dev);

int (*init)(struct adreno_device *adreno_dev);

void (*remove)(struct adreno_device *adreno_dev);

int (*rb_start)(struct adreno_device *adreno_dev);

int (*microcode_read)(struct adreno_device *adreno_dev);

void (*start)(struct adreno_device *adreno_dev);

bool (*is_sptp_idle)(struct adreno_device *adreno_dev);

int (*regulator_enable)(struct adreno_device *adreno_dev);

void (*regulator_disable)(struct adreno_device *adreno_dev);

void (*pwrlevel_change_settings)(struct adreno_device *adreno_dev,

unsigned int prelevel, unsigned int postlevel,

bool post);

int64_t (*read_throttling_counters)(struct adreno_device *adreno_dev);

void (*count_throttles)(struct adreno_device *adreno_dev,

uint64_t adj);

unsigned int (*preemption_pre_ibsubmit)(

struct adreno_device *adreno_dev,

struct adreno_ringbuffer *rb,

unsigned int *cmds,

struct kgsl_context *context);

int (*preemption_yield_enable)(unsigned int *cmds);

unsigned int (*set_marker)(unsigned int *cmds,

enum adreno_cp_marker_type type)