202003024027

Posted 小禹儿

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了202003024027相关的知识,希望对你有一定的参考价值。

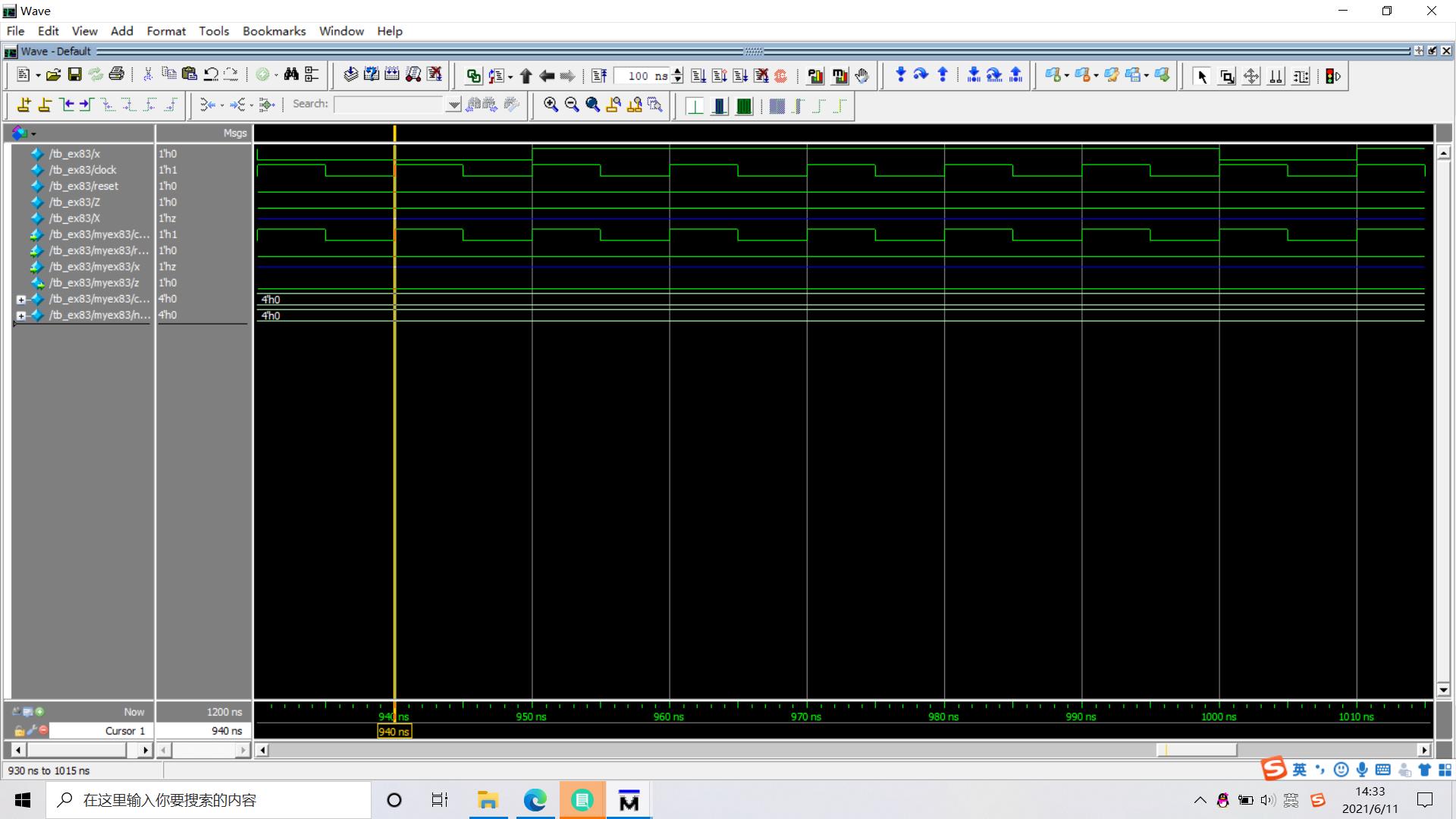

heyuling 14:34:44

module ex8_3 (clock, reset,x,z) ;

input clock, reset;

input x;

output z;

reg z;

reg[3:0] cstate, nstate;

parameter s0=4'd0,s1=4'd1,

s2=4'd2,s3=4'd3,s4=4'd4,s5=4'd5,s6=4'd6;

always @(posedge clock or posedge reset)

begin

if(reset)

cstate<=s0;

else

cstate<=nstate;

end

always @(cstate or x)

begin

case(cstate)

s0:begin

if(x==1)

nstate=s1;

else

nstate=s0;

end

s1:begin

if(x==0)

nstate=s2;

else

nstate=s1;

end

s2:begin

if(x==1)

nstate=s3;

else

nstate=s0;

end

s3:begin

if(x==0)

nstate=s4;

else

nstate=s1;

end

s4:begin

if(x==1)

nstate=s5;

else

nstate=s0;

end

s5:begin

if(x==1)

nstate=s6;

else

nstate=s4;

end

s6:begin

if(x==0)

nstate=s0;

else

nstate=s1;

end

default:nstate=s0;

endcase

end

always @(nstate)

if(nstate==s6)

z=1;

else

z=0;

endmodule

heyuling 14:34:57

module tb_ex83;

reg x,clock, reset;

wire Z;

initial clock=1;

always #5 clock=~clock;

initial

begin

reset=0;

#15 reset=1;

#15reset=0;

#10000 $stop;

end

always #10 x=$random;

ex8_3 myex83(clock, reset,X,Z) ;

endmodule

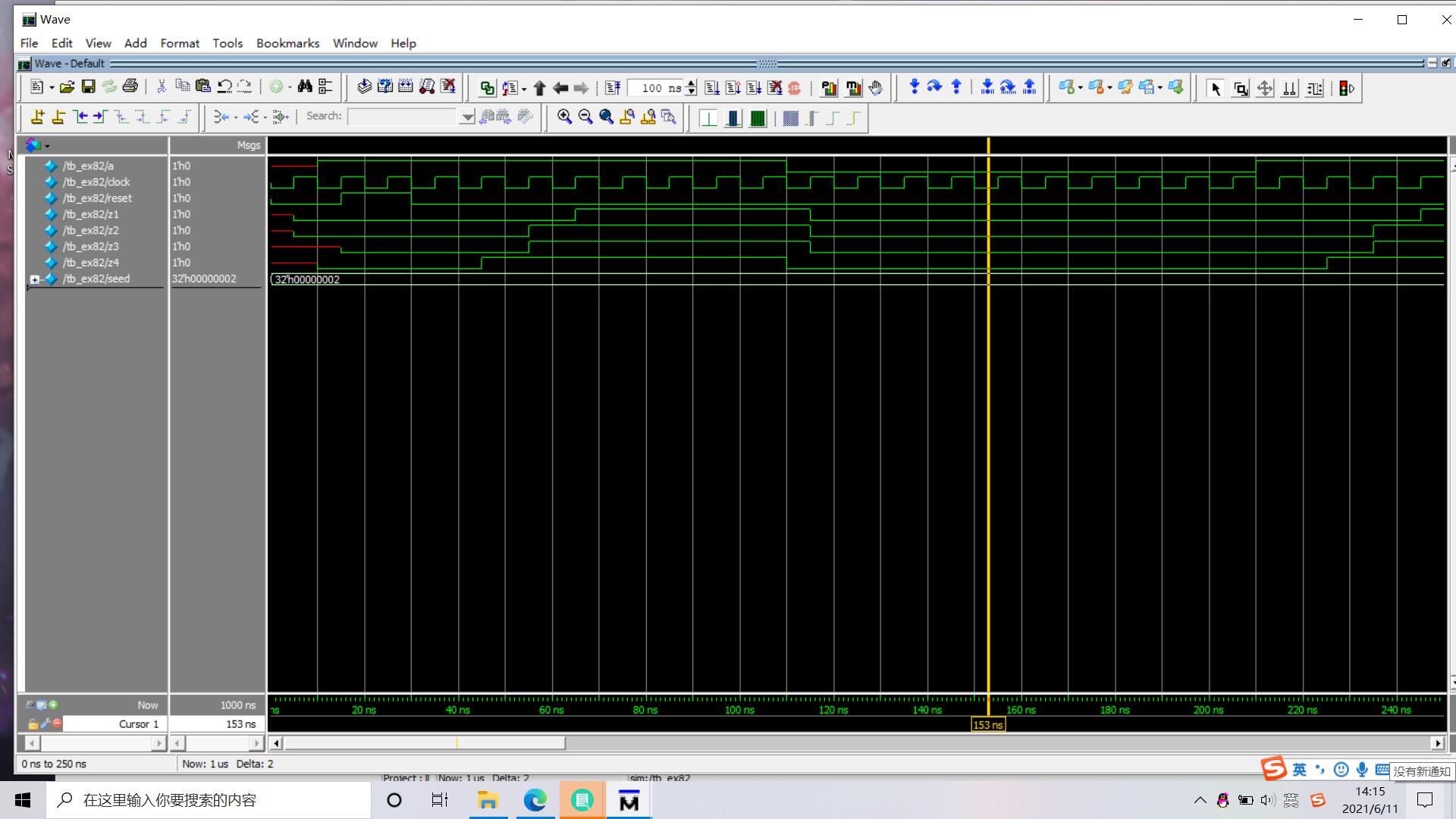

heyuling 14:15:55

module tb_ex82;

reg a,clock, reset;

wire z1,z2, z3, z4;

integer seed=2;

initial clock=0;

always #5 clock=~clock;

initial

begin

reset=0;

#15 reset=1;

#15 reset=0;

#10000 $stop;

end

initial

begin

#10 a=1;

#100 a=0;

#100 a=1;

end

ex8_2 myex82 (clock, reset,a,z1, z2,z3,z4);

endmodule

heyuling 14:16:21

module ex8_2(clock, reset,a,z1,z2,z3,z4);

input clock, reset;

input a;

output z1,z2,z3,z4;

reg z1,z2,z3, z4;

reg [1:0] cs,ns;

parameter s0=2'b00,s1=2'b01,s2=2'b11,s3=2'b10;

always @(posedge clock or posedge reset)

begin

if (reset)

cs<=s0;

else

cs<=ns;

end

always @(cs or a)

begin

case(cs)

s0:begin

if(a==0)ns=s0;

else

ns=s1;

end

s1:begin

if(a==0)

ns=s0;

else

ns=s2;

end

s2:begin

if(a==0)

ns=s0;

else

ns=s3;

end

s3:begin

if(a==0)

ns=s0;

else

ns=s3;

end

default:ns=s0;

endcase

end

always @(posedge clock)

begin

if (cs==s3 && a==1)

z1<=1;

else

z1<=0;

end

always @(posedge clock)

begin

if(ns==s3 && a==1)

z2<=1;

else

z2<=0;

end

always @(cs)

begin

if (cs==s3 && a==1)

z3=1;

else

z3=0;

end

always @(ns)

begin

if(ns==s3 && a==1)

z4=1;

else

z4=0;

end

endmodule

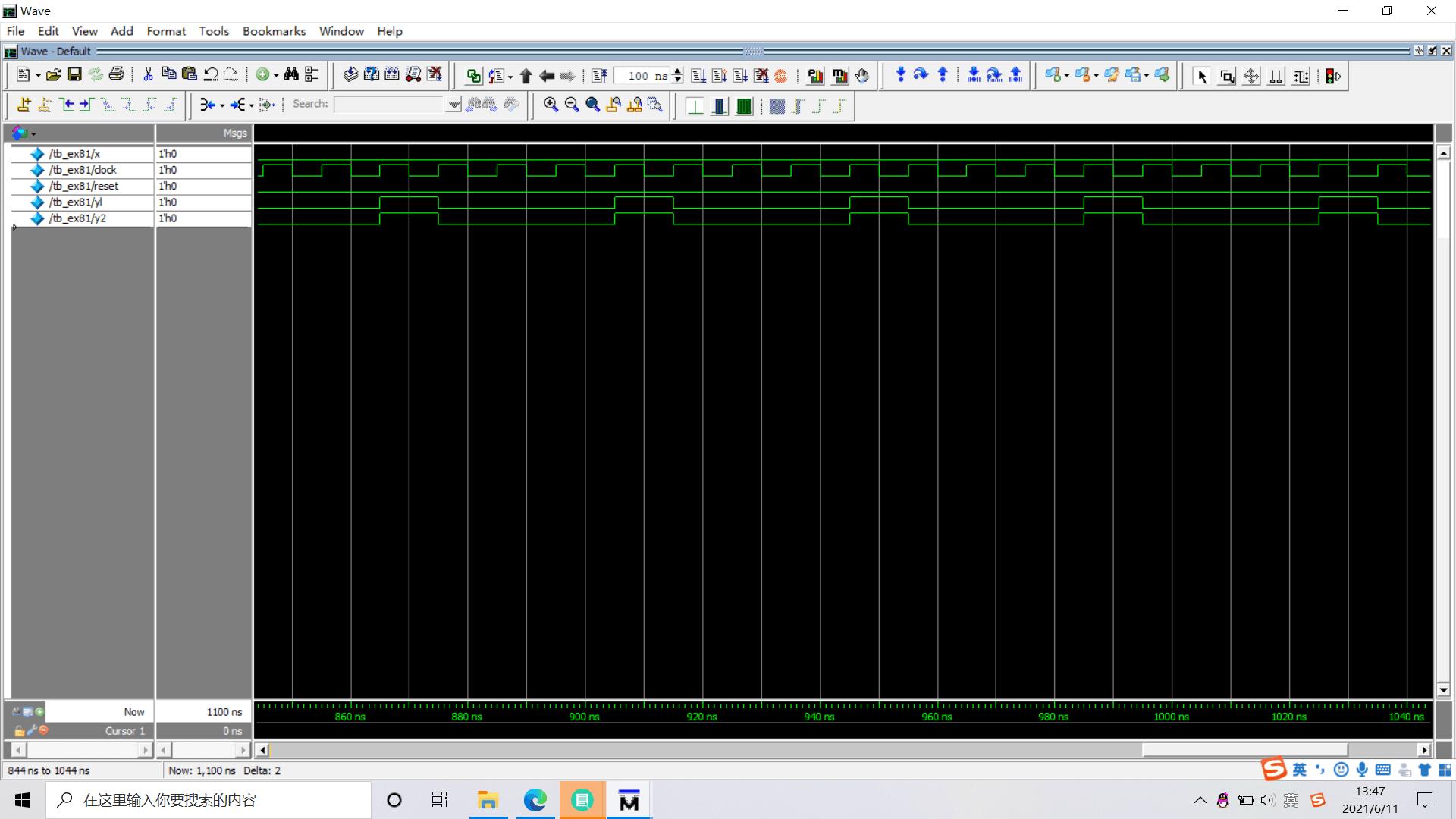

heyuling 13:49:44

module ex8_1(clock,reset,x,y1,y2) ;

input clock,reset;

input x;

output y1,y2;

reg y1,y2;

reg [3:0] cstate,nstate;

parameter s0=4'b0001,s1=4'b0010,

s2=4'b0100,s3=4'b1000;

always @ (posedge clock or posedge reset)

begin

if (reset)

cstate<=s0;

else

cstate<=nstate;

end

always @ (cstate or x)

begin

case (cstate)

s0:begin

if (x==0)

nstate=s1;

else

nstate=s3;

end

s1:begin

if (x==0)

nstate=s2;

else

nstate=s0;

end

s2:begin

if (x==0)

nstate=s3;

else

nstate=s1;

end

s3:begin

if (x==0)

nstate=s0;

else

nstate=s2;

end

default : nstate=s0;

endcase

end

always @ (cstate or x)

begin

case (cstate)

s0 : begin

if (x==0)

y1=1;

else

y1=0;

end

s1 : begin

if (x==0)

y1=0;

else

y1=0;

end

s2 : begin

if (x==0)

y1=0;

else

y1=0;

end

s3 : begin

if (x==0)

y1=0;

else

y1=1;

end

default :y1=0;

endcase

end

always @ (cstate or x)

begin

if (cstate==s0 && x==0)

y2=1;

else if (cstate==s3 && x==1)

y2=1;

else

y2=0;

end

endmodule

heyuling 13:49:56

module tb_ex81;

reg x,clock, reset;

wire yl,y2;

initial clock=0;

always #5 clock=~clock;

initial

begin

reset=0;

#15 reset=1;

#15 reset=0;

#10000 $stop;

end

initial

begin

#10 x=1;

#500 x=0;

end

ex8_1 myex81 (clock, reset,x,yl,y2);

endmodule

以上是关于202003024027的主要内容,如果未能解决你的问题,请参考以下文章