基于FPGA的4x4矩阵键盘控制器verilog开发实现

Posted fpga和matlab

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了基于FPGA的4x4矩阵键盘控制器verilog开发实现相关的知识,希望对你有一定的参考价值。

欢迎订阅《FPGA学习入门100例教程》、《MATLAB学习入门100例教程》

目录

一、理论基础

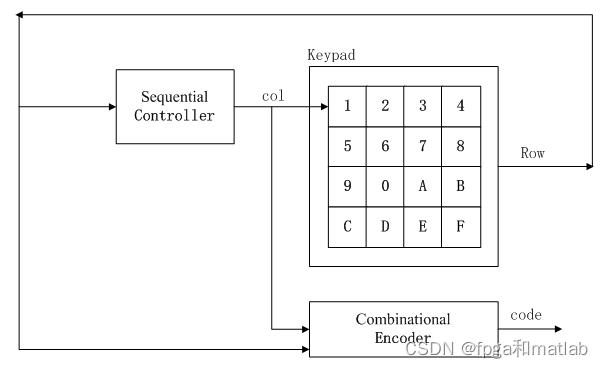

这里第一部分的主要目标是设计一个键盘扫描程序,并读取4*4键盘上的键盘,并以0,1,2,3,4,5,6,7,8,9,A,B,C,D,E,F在7段数码管上显示出来。这里我们将用到开发板的键盘和数码管。本模块分为键盘扫描和数码管显示两个部分。这两个部分非常的简单,这里我们合在一起设计。键盘扫描的其基本原理如下所示:

通过不断的扫描来完成键盘值的确认。注意这里四行和四列的交界初就是您实际中的16个按键,当您按下其中某个按键的时候,列信号y1,y2,y3,y4就会在对应的位置显示出来,比如你按下了第一列第二个按钮,那么就会在第二列的位置产生一个信号,又由于行信号x是一直在快速的扫描的,如果当第二行正好扫描过的时候,同时检测到列信号,这说明这个按钮按下了。这就是键盘扫描的基本原理。

数码管,这里,是7段数码管,其基本结构如下所示:

其一共有7个LED来表示一个数码管。

二、核心程序

/*

1. Wait buttons and identify key position: according to certain frequency with low level circulation scan lines Y3, Y0 -

Monitor the status, once listed line judge a listed as low means have key is pressed,

Stop scans and maintain the current state of lines, then read column line condition to get the current buttons are key code.

2. Wait buttons pop-up: detection to each column line all become the top flat after restarting the scanning process, waiting for the next buttons

�

*/

module key_scanner(

clk,

rst,

row,

column,

scan_key

);

input clk;

input rst;

input [3:0] column;//Column line

output[3:0] row;//lines

output[3:0] scan_key;

reg[3:0] row;

reg[3:0] scan_key; // scan code registers

reg[31:0] cnt_scan;// scan frequency counter

reg sign; //sign=1:stop scanning

// sign=0:restart scanning*/

reg restart; //

always@(posedge clk or negedge rst)

begin

if(!rst)

begin

row<=4'b1110;

cnt_scan<=0;

end

else begin

if(sign==1'b0)

begin

restart<=0;

cnt_scan<=cnt_scan+1;

//if(cnt_scan==32'h0000ffff)

// begin

row[3:1]<=row[2:0];

row[0]<=row[3]; //4 root lines circulation send out low level

// cnt_scan<=0;

//end

end

else if(sign==1'b1)

begin

row<=row;

if(column==4'b1111)

restart<=1;

//Detect each column is high level

end

end

end

always@(posedge clk or negedge rst)

begin

if(!rst)

begin

scan_key<=0;

end

else begin

if(restart)

begin

sign<=0;

scan_key<=0;

end

else begin

case(row) //This case results testing where key press

4'b1110:

case(column)

4'b1110: begin

sign<=1;

scan_key<=0;

end

4'b1101: begin

sign<=1;

scan_key<=1;

end

4'b1011: begin

sign<=1;

scan_key<=2;

end

4'b0111: begin

sign<=1;

scan_key<=3;

end

endcase

4'b1101:

case(column)

4'b1110: begin

sign<=1;

scan_key<=4;

end

4'b1101: begin

scan_key<=5;

sign<=1;

end

4'b1011: begin

scan_key<=6;

sign<=1;

end

4'b0111: begin

scan_key<=7;

sign<=1;

end

endcase

4'b1011:

case(column)

4'b1110: begin

scan_key<=8;

sign<=1;

end

4'b1101: begin

scan_key<=9;

sign<=1;

end

4'b1011: begin

scan_key<=10;

sign<=1;

end

4'b0111: begin

scan_key<=11;

sign<=1;

end

endcase

4'b0111:

case(column)

4'b1110: begin

scan_key<=12;

sign<=1;

end

4'b1101: begin

scan_key<=13;

sign<=1;

end

4'b1011: begin

scan_key<=14;

sign<=1;

end

4'b0111: begin

scan_key<=15;

sign<=1;

end

endcase

default:

scan_key<=15;

endcase

end

end

end

endmodule

三、测试结果

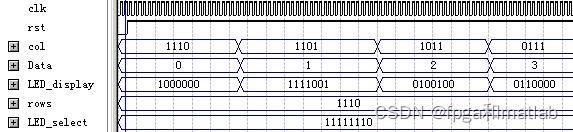

其仿真结果如下所示:

注意col进行扫描的时候,data分别输出0,1,2,3等键盘值。

| Clk | 系统时钟 |

| Rst | 系统复位 |

| Col | 由键盘输入产生的列扫描信号 |

| Data | 键盘值 |

| LED_display | 7LED数值显示 |

| Rows | 行扫描信号 |

| LED_select | 数码管的选择 |

A02-37

以上是关于基于FPGA的4x4矩阵键盘控制器verilog开发实现的主要内容,如果未能解决你的问题,请参考以下文章