原理图与 PCB 绘制备忘

Posted 研究是为了理解

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了原理图与 PCB 绘制备忘相关的知识,希望对你有一定的参考价值。

PCB 绘制

- 考虑到各制板厂的工艺水平的不同,过孔不可过小,最小为

12/25 mil,常用过孔为16/28 mil和24/40mil。 - 铺铜时,与管脚有连接时做成部分相连。这是因为整体相连后,焊接元器件时因为铜皮散热快而难以化开焊锡。

- 英制与公制转换的快捷键是

q键。 - 快捷键

R - M可实现快速测量间距 Ctrl + R可以实现图章工具Shift + S:打开/关闭单层- 按键

E - Origin(原点)- Set可以重设原点 - Altium Designer 16.1 重绘 PCB 外框步骤

AD16 以及高版本的 AD 普通模式下都没有了Redefine Board Shape,推荐的做法是在Keep-Out-Layer层绘制板子外形,把外形选中后,点击菜单Design - Board Shape - Define from selected objects即可。

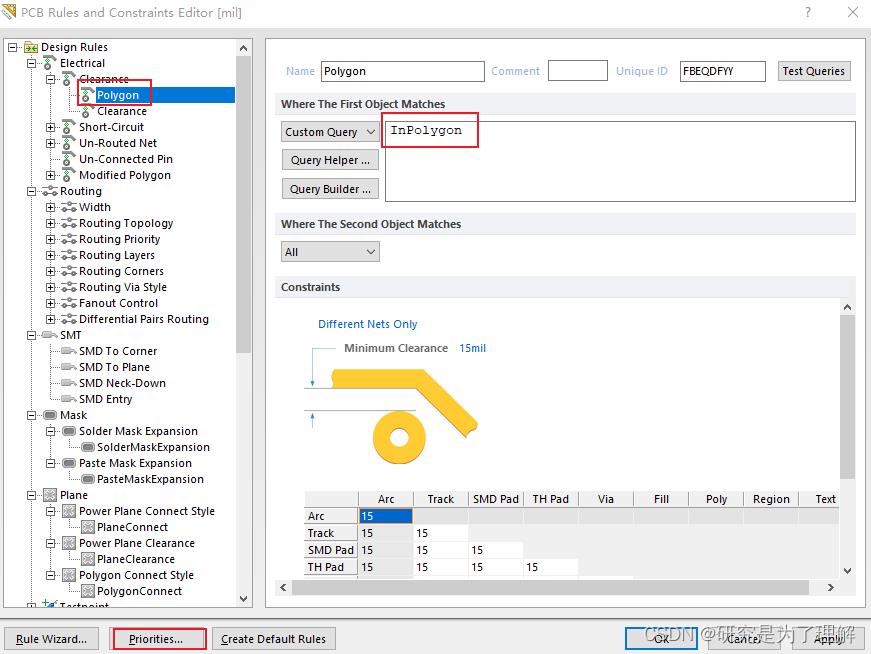

如果还是想像低版本 AD 那样自定义板子外形,在 PCB 界面中按下键盘1,然后点击菜单Design - Redefine Board Shape,现在可以像以前一样自定义绘制 PCB 外形了。绘制完以后,按按键2返回 2D 界面。 - 给铺地专门定义一个规则:打开规则界面,在

Electrical - Clearance上右击,选择New Rule...,新建一个Polygon规则:

然后点击底部Priorities...按钮,将Polygon优先级设置为 1(最高)。 - 添加层:

Design - Layer Stack Manager,在弹出的界面中右键,添加层。

- 保留

PCB 规则检查

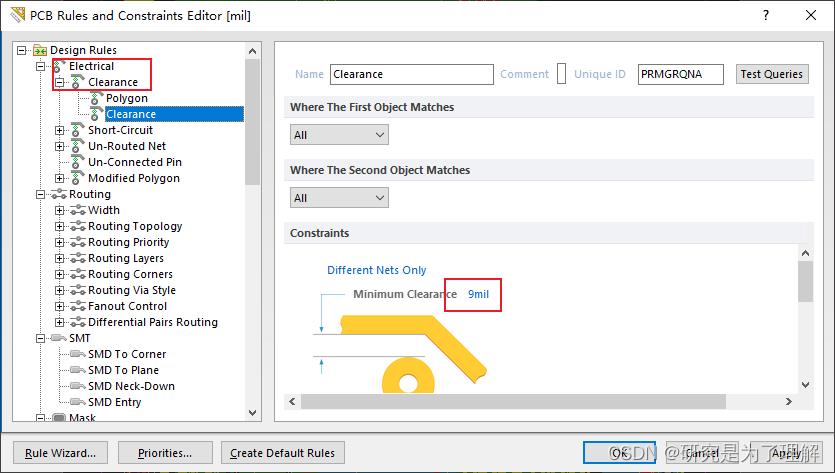

- Clearance Constraint(Gap=9mil):违反电气间隙限制

对应规则中的Electrical - Clearance:

- Un-Routed Net Constraint:有未布线的网络

对应规则中的Electrical - Un-Touted Net

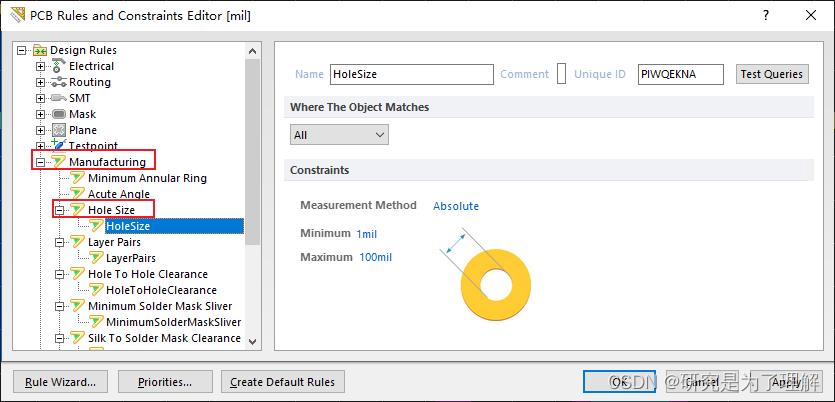

- Hole Size Constraint(Min=1mil)(Max=100mil):违反了孔尺寸大小限制

对应规则中的Manufacturing(制造) - Hole Size:

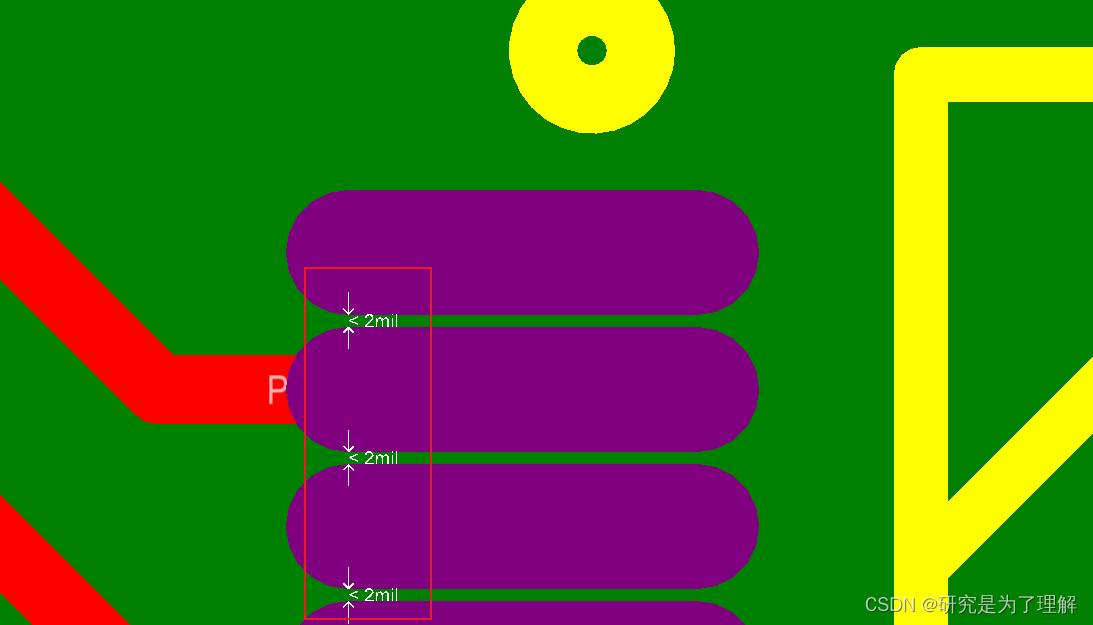

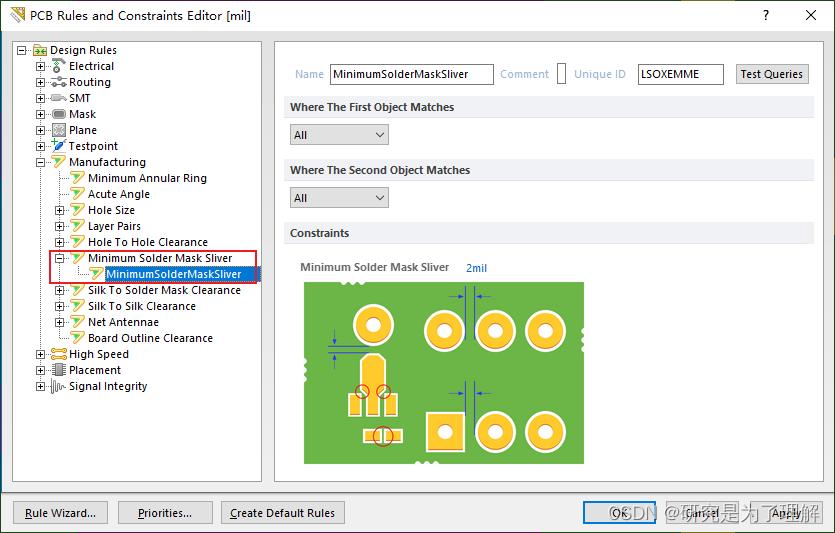

- Minimum Solder Mask Sliver(Gap=2mil):违反阻焊层与阻焊层最小间距

对应规则中的Manufacturing(制造) - Minimum Solder Mask Sliver:

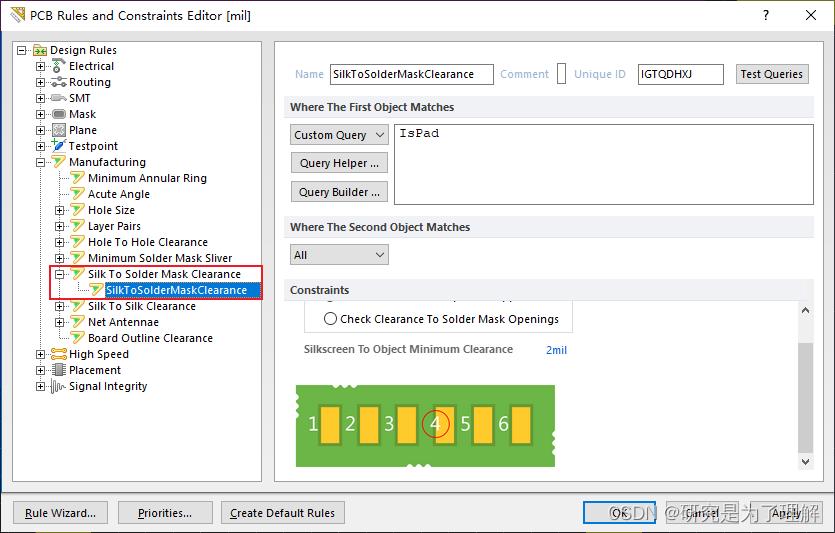

- Silk To Solder Mask(Clearance=2mil):违反丝印到阻焊层最小间距

对应规则中的Manufacturing(制造) - Silk To Solder Mask Clearance:

- Silk to Silk(Clearance=2mil):违反丝印与丝印最小间距

对应规则中的Manufacturing(制造) - Silk To Silk Clearance:

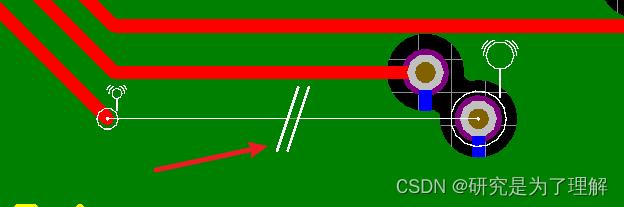

- Net Antennae:走线突出去一部分形成了天线

对应规则中的Manufacturing(制造) - Net Antennae:

- 保留

将 PCB 导出为 PDF

- 点击

File - Smart PDF... - 选择存放位置

- 选择是否导出 BOM

- 进入 PCB 打印输出设置:

在红框中双击鼠标,打开层属性对话框:

- TopOverlay、Mechanical1、Mutti-layer全部保留

注:TopOverlay中去除字符串,指示器和注释, 可以去除丝印字符 - Top Layer层按照如下设置:

其它图层全部关闭

以上是关于原理图与 PCB 绘制备忘的主要内容,如果未能解决你的问题,请参考以下文章