在xilinx ise12.2 环境下用自带的isim仿真详解

Posted yijingjing17

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了在xilinx ise12.2 环境下用自带的isim仿真详解相关的知识,希望对你有一定的参考价值。

学习FPGA写的第一篇文档,算是人生的一个里程碑,现在脑子里是当年一个人在一个实验室默默学习的场景,但最后依靠着这项技能养活自己,感恩

最近项目用到FPGA,也开始了FPGA的学习历程,硬件为红色飓风的E45,FPGA是spartan6系列的,软件开发环境是xilinx ise12.2的版本。

之前一直在做单片机,有一定的C基础,对FPGA的学习也算快吧,花了一天的时间移植了一个FPGA的串口程序,测试通过,收发正常,心里美滋的,在第三天的时候要做一个SPI的时序,由于程序是自己写的,所以对时序没把握,就需要仿真,看一下波形,可谁知道这一仿真就是2天的时间,搞得我头疼闹热的,到处查资料,看网站,弄得我好不痛苦啊,明明很简单的事情,却花了两天的时间,哎,在此也深感一个人学习的痛苦,也感到资源的可贵啊,为了我的两天时间,我决定写下记录,以此让跟我一样遇到问题的人能够少花时间。

以下是我从网上收集的在xilinx ise12.2 环境下用自带的isim仿真步骤:

http://wenku.baidu.com/view/fce6e53c0912a21614792981.html

该链接的资料是OK的,但是有些小的细节需要说了,同时也我遇到的问题。

1. 在生成verilog hex fixture 之后,一定要记得在Add stimulus here之后加上你的动作代码,要不然仿真是不会有动作的,问题很幼稚,但是他花了我2个小时的时间,回头看了好几遍文档在注意到有自己要添加的东西。

一般的添加格式为:

initial

begin

clk= 1'b0;

rst= 1'b0;

#5

clk= 1'b1;

rst= 1'b1;

end

always #10clk = ~clk;

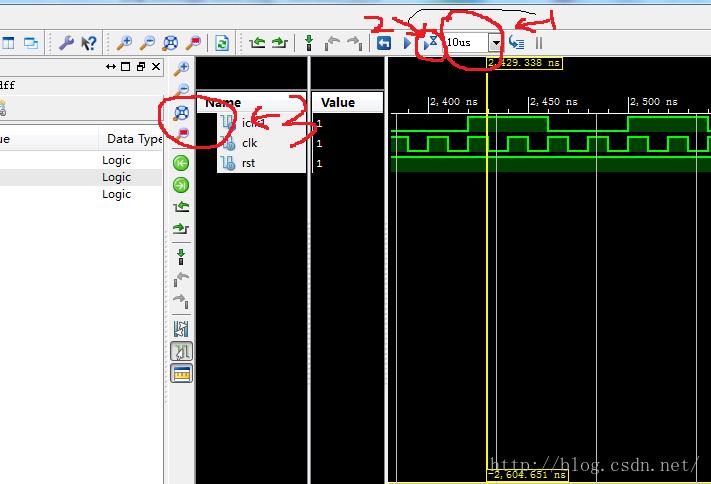

2. 对于isim的界面,需要用好几个工具。

1所指的10us的选项,一般默认都很小,所以要根据具体的时间自己修改,小问题,也花了我不少时间

2所指的功能键是一次运行10us,很有用的

3所指的放大器在看波形的很好用

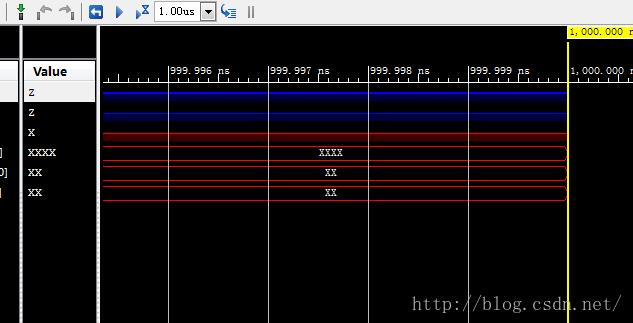

如果仿真出现红线和蓝线,证明仿真失败!

这是我两天以来出现的最多的仿真界面,到现在才明白如果信号不是绿色的证明都是有问题的,仿真是失败的!之所以会出现这种问题都是因为自己的设计功底太差。

3.仿真是程序应该注意的问题.

以下为一段可以正确运行的程序:

module led_run(iClk,oLed);

input iClk;

output [3:0] oLed;

reg [3:0] oLed;

reg [24:0] count;

reg [1:0] state;

wire clk;

always @ (posedge iClk)

count=count+1;

assign clk=count[24];

always @ (posedge clk)

begin

case(state)

2'b00: oLed<=4'b0001;

2'b01: oLed<=4'b0010;

2'b10: oLed<=4'b0100;

2'b11: oLed<=4'b1000;

endcase

state=state+1;

end

endmodule

但是仿真是失败的,原因来自于:没有rst信号。对于count的初始值仿真器无从取得,导致仿真失败。

应该对其做以下修改:

module led_run(iClk,oLed,rst);

input iClk;

input rst;

output [3:0] oLed;

reg [3:0] oLed;

reg [1:0] count;

reg [1:0] state;

wire clk;

always @ (posedge iClk or negedge rst)

begin

if(!rst)

count = 0;

else

count=count+1;

end

assign clk=count[1];

always @ (posedge clk or negedge rst)

begin

if(!rst)

oLed <=4'b0001;

else

begin

case(state)

2'b00: oLed<=4'b0001;

2'b01: oLed<=4'b0010;

2'b10: oLed<=4'b0100;

2'b11: oLed<=4'b1000;

endcase

state=state+1;

end

end

endmodule

对于FPGA的仿真而言,每个值都应该有其初始值,而我恰恰是忽略了这一点。

最后要注意的地方:

仿真时要点击生产的verilog hex fixture文件,而不是其本身的V文件

yi 于2012.02.23

EMEQ实验室

以上是关于在xilinx ise12.2 环境下用自带的isim仿真详解的主要内容,如果未能解决你的问题,请参考以下文章