数字电路 超前进位加法器设计(采用全加器级联)

Posted Ice丨shine

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了数字电路 超前进位加法器设计(采用全加器级联)相关的知识,希望对你有一定的参考价值。

本实验为超前进位加法器,消除了串行加法器运算时间随着加法器位数递增的缺点,用数学推导的方式得出了进位和输入数的关系。

采用四片全加器级联

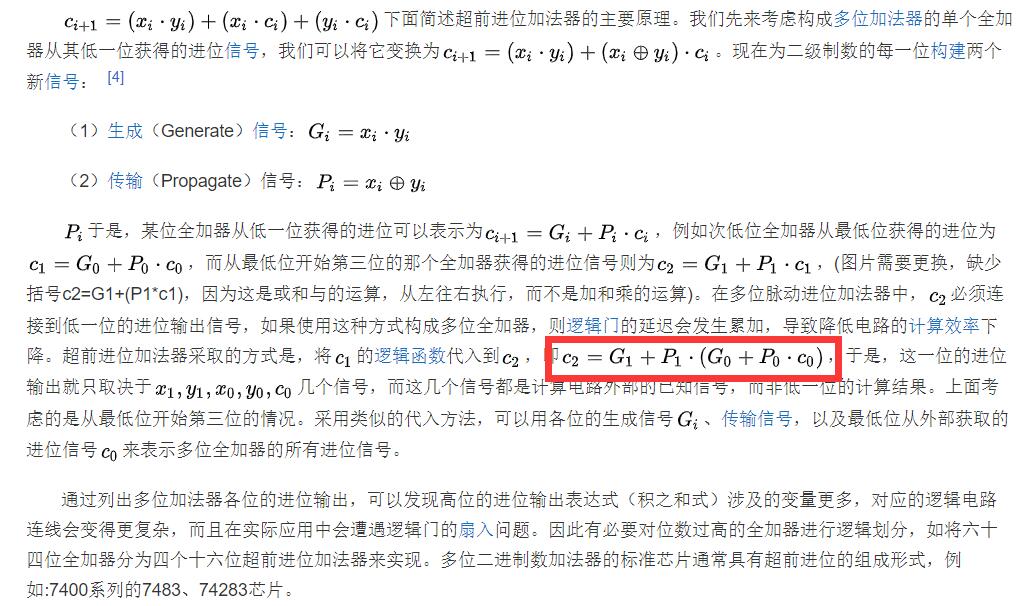

原理部分(来源于百度百科):

(看不懂没关系,直接用红框中的结论就好)

//加法器

module plus(

input A,

input B,

input C1,

output wire F,

output wire C2

);

assign C2,F=A+B+C1;

endmodule

//四位超前进位加法器

module chaoqianadd(

input [3:0]A,

input [3:0]B,

input C0,

output wire C4,

output wire [3:0]F

);

wire C1,C2,C3;

plus p1(

.A(A[0]),

.B(B[0]),

.C1(C0),

.F(F[0]),

.C2(C1)

);

plus p2(

.A(A[1]),

.B(B[1]),

.C1(A[0]*B[0]+(A[0]+B[0])*C0),

.F(F[1]),

.C2(C2)

);

plus p3(

.A(A[2]),

.B(B[2]),

.C1(A[1]*B[1]+(A[1]+B[1])*C1),

.F(F[2]),

.C2(C3)

);

plus p4(

.A(A[3]),

.B(B[3]),

.C1(A[2]*B[2]+(A[2]+B[2])*C2),

.F(F[3]),

.C2(C4)

);

endmodule

测试代码:

`timescale 1ns / 1ps

module chaoqian_t;

// Inputs

reg [3:0] A;

reg [3:0] B;

reg C0;

// Outputs

wire C4;

wire [3:0] F;

// Instantiate the Unit Under Test (UUT)

chaoqianadd uut (

.A(A),

.B(B),

.C0(C0),

.C4(C4),

.F(F)

);

initial begin

// Initialize Inputs

A = 0;

B = 0;

C0 = 0;

// Wait 100 ns for global reset to finish

repeat(512)

#2 A,B,C0=A,B,C0+1;

// Add stimulus here

end

endmodule

仿真波形

以上是关于数字电路 超前进位加法器设计(采用全加器级联)的主要内容,如果未能解决你的问题,请参考以下文章