ARM Cortex-A73 Power management

Posted Wu_Being

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了ARM Cortex-A73 Power management相关的知识,希望对你有一定的参考价值。

The Cortex-A73 processor provides mechanisms and support to control both dynamic and static power

dissipation.

文章目录

Power domains

The Cortex-A73 processor can support multiple power domains. Each power domain has four possible

states.

The Cortex-A73 processor supports the following power domains:

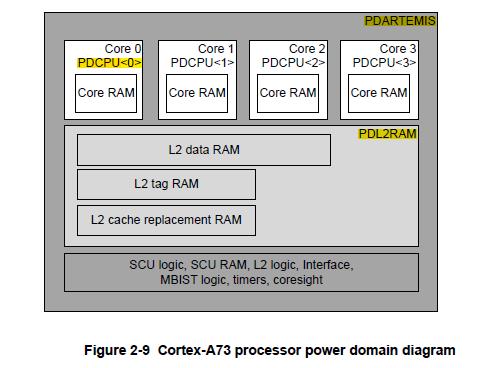

• The top-level domain (PDARTEMIS) including:

— SCU logic and its tag RAM.

— BIST multiplexors and clock modules.

— Various interface modules.

— L2 logic.

— Debug.

• Core 0-3 domain (PDCPU), including RAMs.

• The L2 data, tag, and cache replacement RAM domain (PDL2RAM).

The figure below shows an example of the organization of the power domains.

The Cortex-A73 power domains have the following features:

• Each power domain has a separate controllable clock.

• Except for RAM-related domains, each power domain has a separate controllable reset.

• Each power domain has its own level of hierarchy.

Power modes

The power domains can be controlled independently to give different combinations of powered-up and

powered-down domains.

However, only some power domain state combinations are valid and supported.

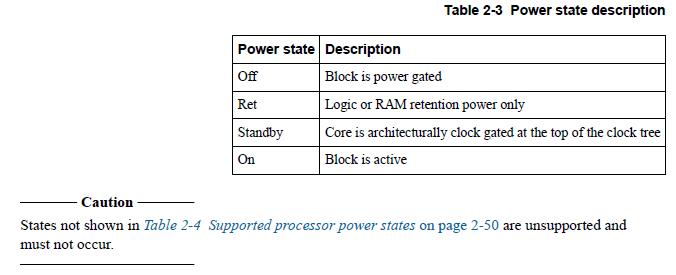

Table 2-4 Supported processor power states on page 2-50 shows the supported power domain states for

the Cortex-A73 processor. The following table defines the terms used.

You must follow the dynamic power management and powerup and powerdown sequences described in

the following sections. Any deviation from these sequences can lead to UNPREDICTABLE results.

摘自:Arm Cortex-A73 MPCore处理器技术参考手册修订版r1p0《cortex_a73_trm_100048_0100_06_en.pdf》

以上是关于ARM Cortex-A73 Power management的主要内容,如果未能解决你的问题,请参考以下文章