Verilog学习笔记

Posted ACheng63201

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了Verilog学习笔记相关的知识,希望对你有一定的参考价值。

文章目录

参考来源:china.pub.com

一、Verilog HDL简介

1.1 Verilog HDL

- Verilog HDL是一种硬件描述语言,用于从算法级、门级到开关级的多种抽象设计层次的

数字系统建模。被建模的数字系统对象的复杂性可以介于简单的门和完整的电子数字系统之

间。数字系统能够按层次描述,并可在相同描述中显式地进行时序建模。

- Verilog HDL 语言具有下述描述能力:设计的行为特性、设计的数据流特性、设计的结构

组成以及包含响应监控和设计验证方面的时延和波形产生机制。所有这些都使用同一种建模

语言。此外,Verilog HDL语言提供了编程语言接口,通过该接口可以在模拟、验证期间从设

计外部访问设计,包括模拟的具体控制和运行。

二、HDL指南

2.1 模块(module)

- 基本语法:

- 说明部分语句最好放在module开头部分

- 端口默认大小为一位,线网型(线网类型表示构件间的物理连线,而寄存器类型表示抽象的数据存储元件。)

module module name (port list)i

Declarations

reg, wire, parameter,

input, output, inout

function, task,

statements

Initial statement

Always statement

Module ins tantiation

Gate instantiation

UDP instantiation

Continuous assignment

endmodule

2.2时延

`` timescale** 1ns /100ps`编译器指令在模块描述前定义,表示时延时间单位为 1 n s并且时间精度为100ps

#2表示2个时间单位

2.3数据流描述方式

- 连续赋值语句

- 语法:

assign [delay] LHS_net = RHS_ expression - 右表达式使用的操作数一旦发生变化 , 右边表达式都重新计算 , 在指定的时延后变化值(默认为0)被赋予左边表达式的线网类型变量。

- 连续赋值语句只能为线网类型变量赋值

- 连续赋值语句是并发执行的,各语句的执行顺序与其在描述中出现的顺序无关

- 语法:

2.4行为表述方式

-

initial语句

- 只执行一次

-

always语句

-

循环执行

-

语法:’,'和“or”都可以分割敏感事件,可以用“*”代表所有输入信号,always 语句中有一个与事件控制(紧跟在字符@ 后面的

表达式)。相关联的顺序过程( begin - end对)。

always@ * always@ (posedge clk1,negedge clk2) always@ (a or b) begin //顺序过程 end -

在顺序过程中出现的语句是过程赋值模块化的实例。模块化过程赋值在下一条语句执行前完成执行。过程赋值可以有一个可选的时延。分为语句间(时延语句执行的时延)、内(右边表达式数值计算与左边表达式赋值间的时延)时延

-

-

寄存器类型数据能够在这两种语句中被赋值。寄存器类型数据在被赋新值前保持原有值不变。

-

所有的初始化语句和 always语句在0时刻并发执行。

2.5 结构化描述形式

- 内置门原语(在门级);XOR,OR,AND

- 开关级原语(在晶体管级);

- 用户定义的原语(在门级);

- 模块实例 (创建层次结构)。

2.6混合设计描述方式

- 模块描述中可以包含实例化的门、模块实例化语句、连续赋值语句以及 always语句和initial语句的混合。它们之间可以相互包含。来自 always语句和initial语句(切记只有寄存器类型数据可以在这两种语句中赋值)的值能够驱动门或开关,而来自于门或连续赋值语句(只能驱动线网)的值能够反过来用于触发always语句和initial语句。

三、Verilog语言要素

3.1标识符

- 标识符是任意一组字母、数字、 $符号和_(下划线)符号的组合,但第一个字符必须是字母或者下划线。标识符区分大小写。

- 转义标识符在一条标识符中包含任何可打印字符。转义标识符以 \\ (反斜线)符号开头,以空白结尾

3.2 注释

-

/ *第一种形式:可以扩展至 多行 * / / /第二种形式:在本行结束。

3.3编译指令

| 指令 | 使用 | 含义 |

|---|---|---|

define** | ** define MAX _BUS _SIZE 3 2 | 用于文本替换,它很像 C语言中的#define 指令 | |

undef** | ** undef MAX _BUS _SIZE 3 2 | 指令取消前面定义的宏。 | |

ifdef else 、endif |  | 条件编译 |

default_nettype** | **default_nettype wand | 令用于为隐式线网指定线网类型。是将那些没有被说明的连线定义线网类型。 | |

include** | ** include " . . / . . /primitives.v | 用于嵌入内嵌文件的内容。文件既可以用相对路径名定义,也可以用全路径名定义 | |

resetall** | **resetall | 将所有的编译指令重新设置为缺省值。 | |

timescale** | ** timescale time _ unit / time _ preciso | 用于定义时延的单位time _ unit和时延精度time _ preciso |

3.4 值集合

| 值 | 0 | 1 | z | x |

|---|---|---|---|---|

| 含义 | 逻辑0或“假” | 逻辑1或“真” | 高阻 | 未知 |

- 字符串的表示方式:字符串是双引号内的字符序列。字符串不能分成多行书写。用8位A S C I I值表示的字符可看作是无符号整数。

“INTERNAL ERROR”

reg [1:8*14] Message;

3.5 数据类型

3.5.1线网类型

-

语法:

net_kind[msb:lsb] net1, net2, . . . ,netN; -

net _kind 是线网类型。 msb和lsb是用于定义线网范围的常量表达式;范围定义是可选的,缺省的线网类型为 1位。

-

类型

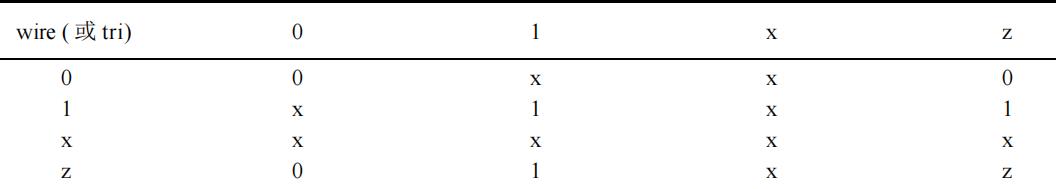

类型 含义 有效值表 wire和t r i线网 用于连接单元的连线是最常见的线网类型。三态线可以用于描述多个驱动源驱动同一根线的线网类型;

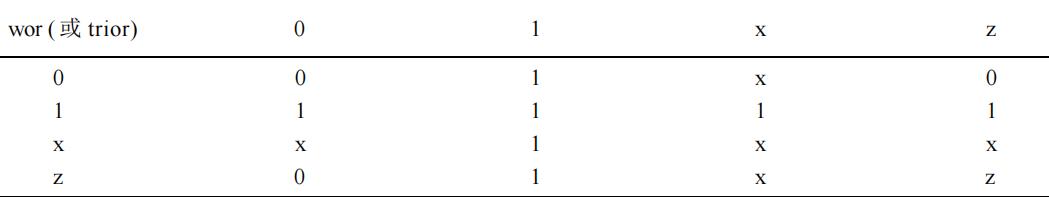

wor和t r i o r线网 线或指如果某个驱动源为 1,那么线网的值也为 1。

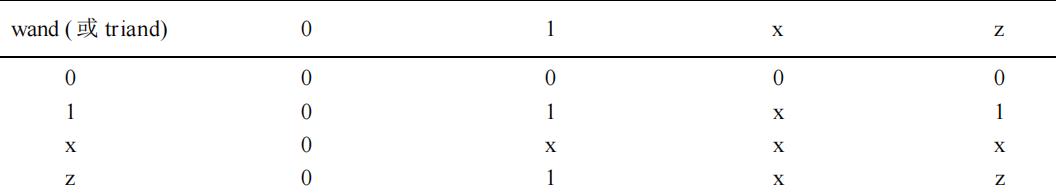

wand和t r i a n d线网 线与( w a n d )网指如果某个驱动源为 0,那么线网的值为 0。

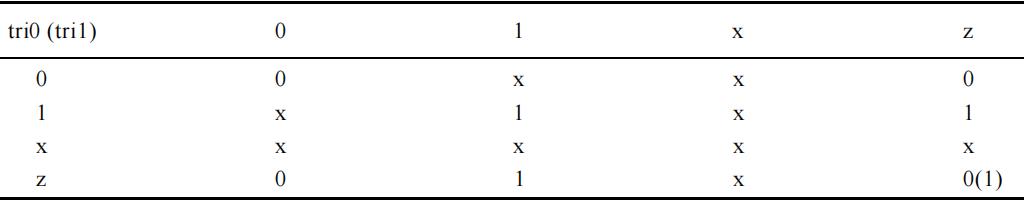

trireg线网 此线网存储数值(类似于寄存器),并且用于电容节点的建模。当三态寄存器 ( t r i r e g )的所有驱动源都处于高阻时,三态寄存器线网保存作用在线网上的最后一个值。三态寄存器线网的缺省初始值为 x。 tri0和t r i 1线网 这类线网可用于线逻辑的建模,即线网有多于一个驱动源。

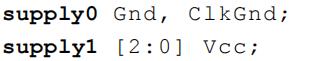

supply0、supply1线网 s u p p l y 0用于对“地”建模,即低电平 0;s u p p l y 1网用于对电源建模,即高电平 1;

3.5.2 寄存器类型

| 类型 | 使用 | 含义 |

|---|---|---|

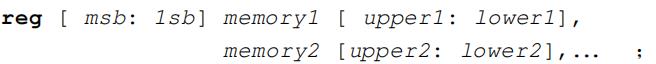

| reg | reg [ msb: lsb] reg1, reg2, . . . r e g N; | reg是最常见的数据类型。msb和l s b 定义了范围。范围定义是可选的;缺省值为1位寄存器。 |

| 存储器 |  | 数组的维数不能大于 2。注意存储器属于寄存器数组类型。 |

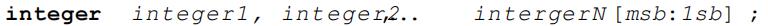

| Integer |  | 缺省32位。整数不能作为位向量访问。种截取位值的方法是将整数赋值给一般的 r e g类型变量,然后从中选取相应的位 |

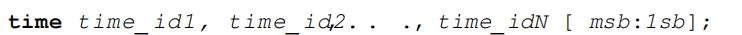

| time |  | time类型的寄存器用于存储和处理时间。缺省64位。只存储无符号数。 |

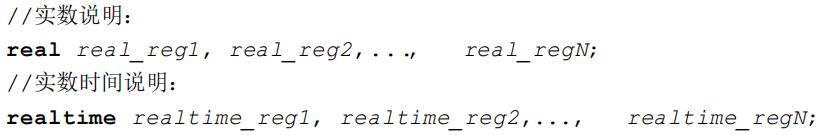

| real和realtime |  | realtime与real类型完全相同。r e a l说明的变量的缺省值为0。不允许对r e a l声明值域、位界限或字节界限。 |

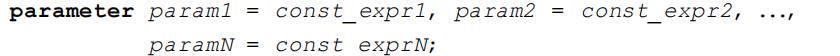

3.6参数

- 参数是一个常量。参数经常用于定义时延和变量的宽度。使用参数说明的参数只被赋值一次。

- 语法:

四、表达式

4.1操作数

-

操作数类型:

-

常数

-

参数

-

线网

-

寄存器

-

位选择

-

部分选择

-

存储器单元

-

函数调用

-

-

如果选择表达式的值为x、z,或越界,则位选择、部分选择的值为 x

-

位选择

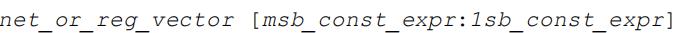

- 位选择从向量中抽取特定的位。net _or_reg _vector [bit _select _expr]

-

部分选择

- 在部分选择中,向量的连续序列被选择,范围表达式必须为常数表达式。

-

存储器单元

-

存储器单元从存储器中选择一个字。memory [word _address]

-

不允许对存储器变量值部分选择或位选择。在存储器中读取一个位或部分选择一个字的方法如下:将存储器单元赋值给寄存器变

量,然后对该寄存器变量采用部分选择或位选择操作。

-

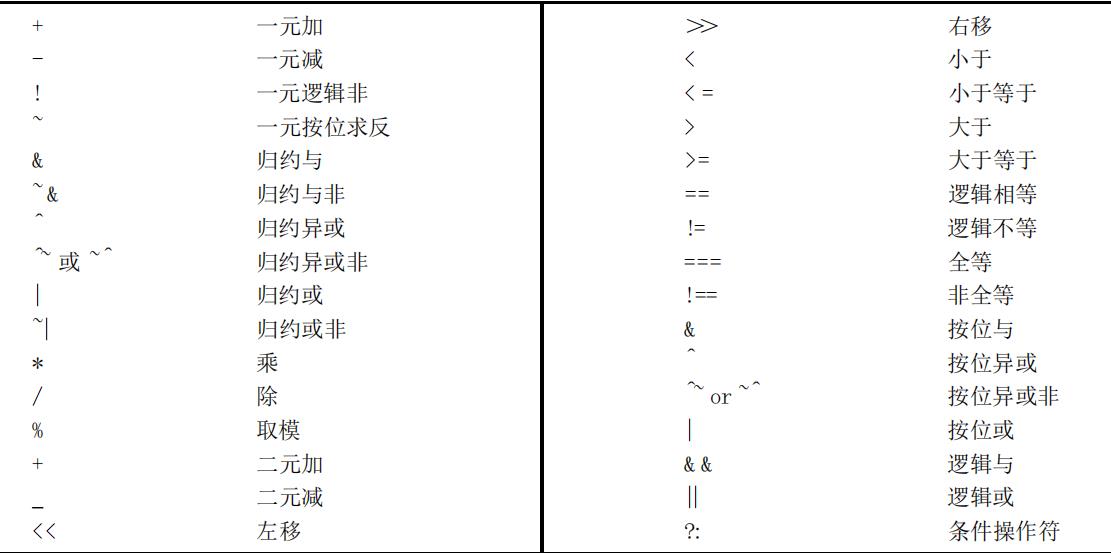

4.2操作符

-

优先级。下表显示了所有操作符的优先级和名称。

操作符从最高优先级(顶行)到最低优先级底行)排列。同一行中的操作符优先级相同。

除条件操作符从右向左关联外,其余所有操作符自左向右关联。

-

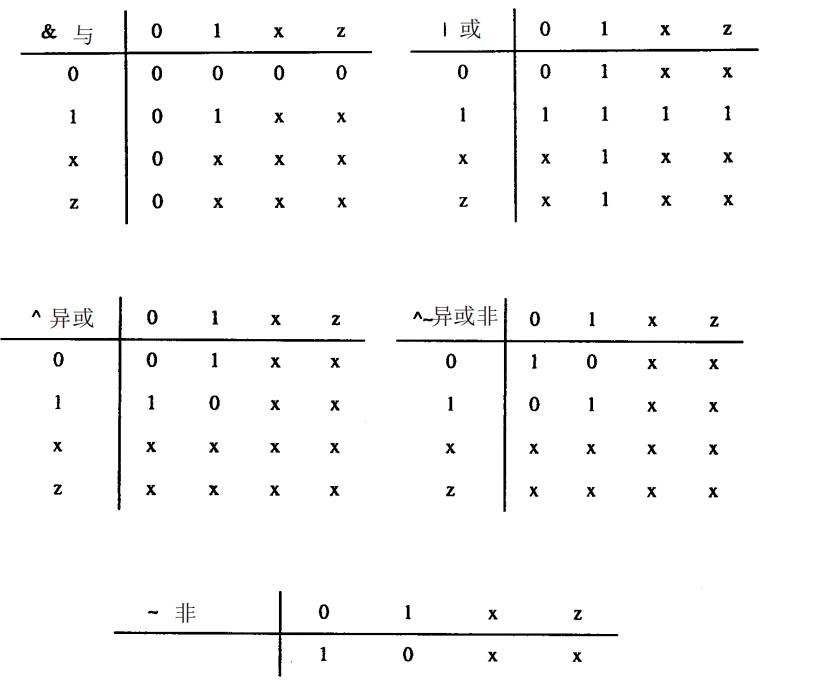

按位操作符,有效值表

-

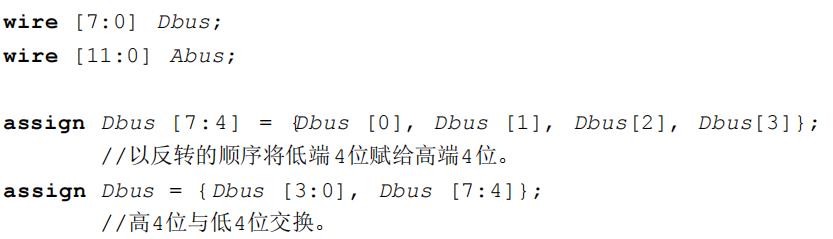

连接和复制操作

-

连接操作是将小表达式合并形成大表达式的操作

-

形式 e x p r 1, e x p r 2, . . .,e x p r N

-

由于非定长常数的长度未知 , 不允许连接非定长常数。

-

实例

-

-

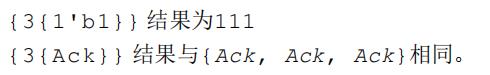

复制通过指定重复次数来执行操作。

-

形式:repetition_number expr1, expr2, …,exprN

-

实例

-

-

以上是关于Verilog学习笔记的主要内容,如果未能解决你的问题,请参考以下文章