集成电路模拟版图入门-版图基础学习笔记

Posted IC观察者

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了集成电路模拟版图入门-版图基础学习笔记相关的知识,希望对你有一定的参考价值。

今日接着给大家分享模拟版图入门学习笔(六),前几期的学习笔记如下:

集成电路模拟版图入门-版图基础学习笔记(一)

集成电路模拟版图入门-版图基础学习笔记(二)

集成电路模拟版图入门-版图基础学习笔记(三)

集成电路模拟版图入门-版图基础学习笔记(四)

集成电路模拟版图入门-版图基础学习笔记(五)

另外大家也可以直接下载完成的源文件:模拟ic版图设计资料

第四部分:版图设计艺术

3.匹配

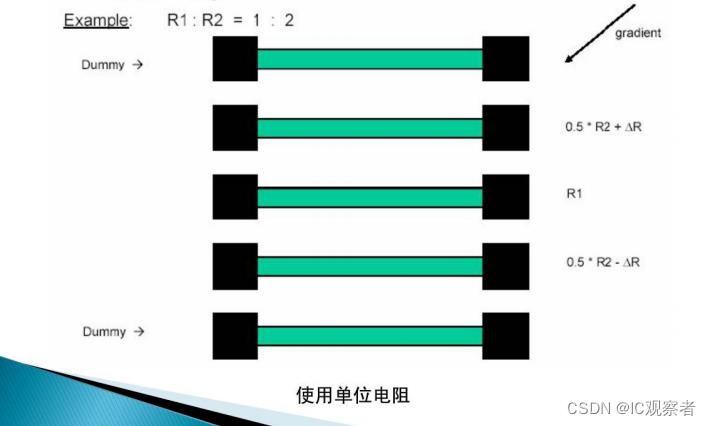

3.5电阻

3.匹配

3.5电阻–叉指结构

3.匹配

3.6电容

3.6.1电容匹配

右图为一个电容中心版图的布局。一片容性组由比率为1:2:4:8:16的电容组成,右图的布局方法使全局误差被均化。

3.7匹配规则

1)把匹配器件相互靠近放置;

2)使器件保持同一个方向;

3)选择一个中间值作为你的根器件;

4)采用指状交叉方式;

5)用虚设器件包围起来;

6)四方交叉你的成对器件;

7)匹配你布线上的寄生参数

8)使每一样东西都很对称;

9)使差分布线一致;

10)使器件宽度一致;

11)总是与你的电路设计者交流;

12)注意邻近的器件;

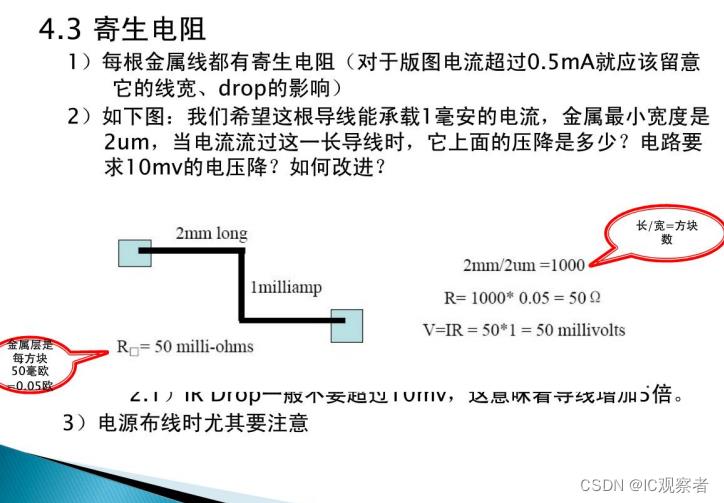

4.寄生效应

4.1寄生的产生

1)两种材料之间会有寄生电容2)电流流过之处会有寄生电阻

3)高频电路导线具有寄生电感

4)器件自身也有寄生效应

5)影响电路的速度,改变频响特性

4.2寄生电容

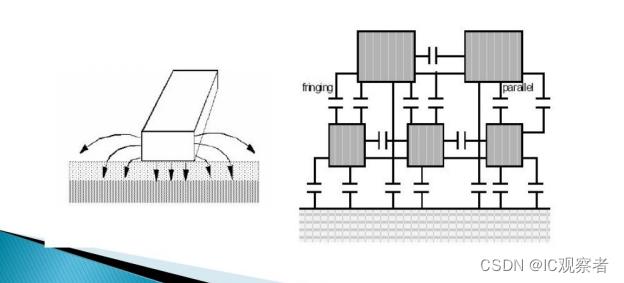

1)金属与衬底之间的平板电容

最重要的寄生问题

通过衬底耦合到其它电路上

2)金属线之间的平板电容

3)金属线之间的边缘电容

4.2寄生电容

4)特定的工艺中,随着金属层次越高,最小宽度越大。M1离衬底最近,单位面积电容越大。M4走供电总线,M3用作二级供电,如下图所示M2的寄生电容最小。

4.2寄生电容

4.2.1减小寄生电容的方法

寄生电容=金属线宽X金属长度X单位面积电容

1)敏感信号线尽量短

2)选择高层金属走线

最高层金属,离衬底最远,单位面积电容最小

3)敏感信号彼此远离

4)不宜长距离一起走线

5)电路模块上尽量不要走线

6)绕开敏感节点

4.6闩锁效应

- Latch up是指cmos晶片中,在电源powerVDD和地线CND之间由于寄生的PNP和NPN双极性BJT相互影响而产生的一低阻抗通路,它的存在会使VDD和GND之间产生大电流。

- Latchup最易产生在易受外部干扰的I/O电路处,也偶尔发生在内部电路。

3.随着IC制造工艺的发展,封装密度和集成度越来越高,产生Latch up的可能性会越来越大。 - Latchup产生的过度电流量可能会使芯片产生永久性的破坏,Latchup的防范是ICLayout的最重要措施之一。

- Latchup的原理分析(二)

**·**Q1为一垂直式PNPBJT,基极(base)是nwell,基极到集电极

(collector)的增益可达数百倍;Q2是一侧面式的NPNBJT,基极为P substrate,到集电极的增益可达数十倍;Rwell是nwell的寄生

电阻;Rsub是substrate电阻。

**·**以上四元件构成可控硅(SCR)电路,当无外界干扰未引起触发时,两个BJT处于截止状态,集电极电流是C-B的反向漏电流构成,电流增益非常小,此时Latch up不会产生。

**·**当其中一个BJT的集电极电流受外部干扰突然增加到一定值时,会反馈至另一个BJT,从而使两个BJT因触发而导通,VDD至GND间形成低抗通路,Latch up由此而产生。

在这里插入图片描述

以上就是关于集成电路模拟的入门分享,欢迎大家咨询留言。

以上是关于集成电路模拟版图入门-版图基础学习笔记的主要内容,如果未能解决你的问题,请参考以下文章