国产EDA与FPGA芯片验证方案

Posted 深圳信迈科技DSP+ARM+FPGA

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了国产EDA与FPGA芯片验证方案相关的知识,希望对你有一定的参考价值。

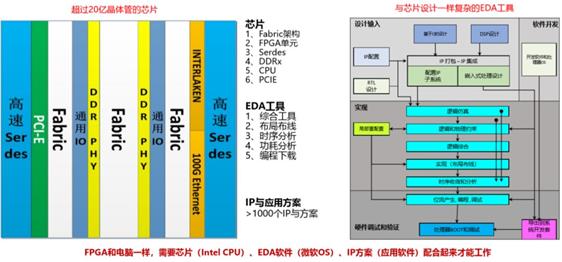

制约FPGA发展的关键技术-EDA

被誉为“万能芯片”的FPGA,近年来越来越多的受到国内市场的关注。不过,其技术门槛之高,在芯片领域几乎是无出其右的。其中,在制约FPGA发展的众多因素中,最关键的便是EDA软件工具。

缺一不可!发展FPGA需软硬件两手抓

FPGA全称为Field Programmable Array,是通过可编程互连连接的可配置逻辑块(CLB) 矩阵构成的可编程半导体器件。FPGA需要配套软件将用户设计烧录到芯片上才能实现相应功能。

目前,在芯片市场主要有CPU、GPU、FPGA与ASIC四大类型。与其它主流芯片相比,FPGA的的灵活性要高于专用芯片ASIC,性能和实时处理能力优于CPU,无需NRE成本,上市时间也更快。不过,其功耗、成本、尺寸都大于专用芯片ASIC,应用开发门槛偏高,并不适合海量应用。

知名半导体专家(《芯事》作者)谢志峰博士认为:“发展FPGA必须在硬件和软件两方面共同发展,如果国内芯片制程工艺达不到要求,FPGA产业很难达到最先进的水平。”

听过了太多国产EDA工具、FPGA芯片的报道,很全面,也都能站在国家战略,资本市场等多个宏观角度去思考、分析问题。但我想,对于普通开发者而言,我们当然相信前途是很美好的,但我们也很关心EDA工具是否稳定(500M的芯片,跑不了50M的逻辑,EDA工具都经历了什么?),简单的逻辑就导致布线的拥塞?在线逻辑分析仪抓不到想要的信号?

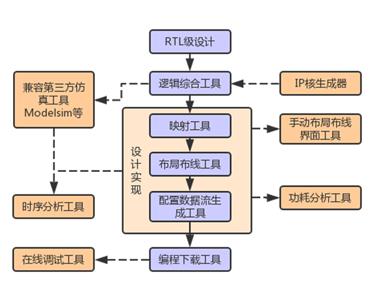

FPGA软件工具设计流程图

如今,国内FPGA产业正处于低端向中高端过渡的关键时期,国内企业已经意识到软件工具自主化的重要意义,并逐步加大投入力度。

随着国家、各地政府对集成电路产业尤其FPGA产品的大力扶持,国内半导体产业链的不断成熟完善,以及新兴市场需求的增大,我们期待着有更多的国产FPGA企业能够在软件工具方面长风破浪,不断突破,抓住市场增量,推进国产FPGA的进一步发展!

1.1 流程1—原理图设计:初步实现芯片功能设计

原理图设计是指暂且不考虑电阻、电容等物理性质,用电路原理图的形式表述芯片功能。原理图设计可以分为顶层 (Top-level)设计与器件(Device-level)设计两个环节。 顶层设计:将各模块(如放大器、滤波器等)连接成电路原理图,满足芯片功能要求; 器件设计:对晶体管等元器件进行定制化设计,满足顶层设计中各模块的功能要求。 原理图设计阶段仅涉及模块间的逻辑关系,暂不考虑电阻、电容等物理问题。

1.2 场景1—射频:定制化设计解决高频环境对芯片的影响

射频信号属于模拟信号的一个子类,与普通模拟芯片设计的区别在于,射频器件所处的高频环境会影响芯片的信号完整 性,加大了芯片设计的难度。射频芯片与模拟芯片:射频芯片的设计与模拟芯片的设计方法基本一致。射频信号本质上是更高频的电磁信号,频率一 般位于30KHz~300GHz之间,而普通芯片处理的交流电频率在50Hz~60Hz之间。 射频芯片设计关注的重点:射频芯片主要应用在通信场景,更关注噪音、失真等干扰因素对芯片的影响。一方面,芯片 的信号会受到各类噪音的干扰,其中包括晶体管和电阻带来的本征噪声,也包括电源、PCB等带来的外部噪声;另一方 面,随着信号频率提高,射频芯片电路的物理性质将可能发生变化,产生一系列寄生效应。

1.3 特点1:前后环节关联紧密,全流程解决方案占优

从设计流程角度看,全定制设计各环节之间关联紧密,具备全流程工具者更具优势。 数字芯片vs模拟芯片:数字芯片设计是一个离散的过程,各个环节之间相对独立;模拟芯片设计是一个连续的过程,设 计、仿真等环节之间存在重叠,可能出现模块的生成、布局与走线在同一阶段完成的情况;从EDA工具的角度看,全定制设计EDA产品间的交互关系也更为紧密。全流程解决方案能够充分发挥产品间的协同作 用,是致力于全定制设计的EDA厂商的重点发力方向。

二、下游需求:覆盖下游近七成市场,EDA工具或占半壁江山

2.1 整体规模:下游市场占比近七成,EDA工具或占半壁江山

全定制设计方法覆盖的半导体市场规模近4000亿美元,占比近七成。 市场规模:据WSTS数据显示,2021年,全球半导体器件销售额5,559亿美元,其中逻辑电路销售额1,548亿美元,其他 半导体销售额合计约4,011亿美元,占比约72.15%; 市场格局:行业集中度高。据IC Insights数据显示,2021年Top 10占比达57.1%,三星与英特尔占比分别达13.3%与 12.5%。 全定制设计EDA工具存在广阔下游市场空间。我们判断全定制类EDA工具占比EDA工具比例近半壁江山,其重要性不言 而喻。

2.2 技术方向1:高频信号对物理验证提出挑战

毫米波作为一种传输率高,带宽大,待用空间广的信号,适用于AR/VR、自动驾驶等多个领域,毫米波芯片成为当前半 导体行业的重点研究对象之一。 市场情况:毫米波频率在30GHz~300GHz之间,过去主要应用在相控阵等军用领域,随着5G通讯的发展,毫米波的民 用市场被逐渐打开。2022年3月,华为发布首款毫米波AI超感传感器,4月,联发科与中华电信宣布合作打造5G毫米波 芯片测试环境; 设计挑战:随着信号频率的进一步提升,信号的寄生效应与串扰等问题将要求相应的仿真与验证技术进一步发展。在此 背景下,当前全定制设计EDA的技术能力仍有较大的提升空间,对EDA工具也提出了新要求,带来更加广阔的市场空 间。

三、产品对比:Cadence整体领先,国内龙头厂商能力接近

3.1 整体格局:三大厂商产品能力位于第一梯队

Cadence、Synopsys与Mentor占据行业龙头地位,射频等细分领域存在局部领先厂商。 Cadence:定制设计EDA领域的领导者,一体化的定制/模拟/混合信号前后端设计平台Virtuoso和仿真器Spectre系列市 占率稳居第一; Synopsys:传统优势在数字芯片设计领域,自收购Avanti等公司后,不断补全模拟领域前后端产品能力,并推出 Hspice仿真器等颇具竞争力的点工具; Mentor Graphics:物理验证能力领先,但整体市占率相对较小,已被西门子收购。部分厂商在细分领域拥有相对较高的技术壁垒,包括射频领域的KeySight、ANSYS以及SILVACO等,PCB领域的 Altium等。

3.2 主要环节:设计平台、电路仿真、物理验证三大方向

全定制EDA工具覆盖原理图及版图设计、电路仿真、物理验证等主要环节,是验证EDA公司核心竞争力的三大重要方向。 电路仿真工具用于验证电路能否正确实现其功能,物理验证工具用于验证版图的物理属性与几何参数,原理图与版图设计 工具则同时也是集成仿真与验证功能的平台。

3.3 设计平台:市场集中度高,Cadence占据先发优势

设计平台环节市场集中度相对较高,其中Cadence Virtuoso平台为全定制设计领域主流设计平台,拥有牢固的市场基 础。 当前全球主流的设计平台主要包括Cadence的Virtuoso以及Synopsys的Custom Compiler。在细分领域,Altium Designer(PCB)、KeySight Pathwave ADS(射频)等也有一定的市场基础。

3.4 电路仿真:不同领域市场格局存在差异

Cadence Spectre系列在模拟/混合信号仿真中处于行业领导者的地位,在SPICE仿真工具中拥有最高的市场渗透率,但 射频、光电等场景各有千秋。 主流产品:海外主流仿真软件为Cadence的Spectre系列与Synopsys的PrimeSim系列。Cadence的Spectre仍为主流模拟/混合信号仿真工具中的领导者。根据Sodido Design Automation(加拿大EDA公司) 对北美芯片设计工程师(2015年317人,2016年246人)的问卷调查,Cadence Spectre是SPICE仿真工具中市场渗透 率最高的品牌。 在细分领域中,部分第二梯队厂商占据了相对优势。例如,射频领域主要使用的包括KeySight Pathwave、ANSYS HFSS,光学领域应用较多的为ANSYS Lumerical。

DSP+ARM+FPGA国产芯片DDR3/DDR4 SI+PI协同仿真分析

3.5 物理验证:Calibre为市场主流物理验证套件

物理验证为对设计结果的最后复核,头部厂商均形成了成熟的物理验证套件,其中Mentor Graphics的Calibre为市场主 流产品。细分环节:物理验证环节本质上是对芯片设计约束的复核,检查芯片版图在技术、功能实现以及几何参数等方面是否符 合设计要求。因而物理验证一般包括DRC、LVS、PEX以及可靠性、可制造性分析等多个子环节; 市场格局:三家EDA龙头厂商已形成了较为全面的物理验证套件,其中Mentor的Calibre、Cadence的PVS以及 Synopsys的StarRC等是物理验证环节主流的系列产品,Calibre拥有较高的市场占有率。

3.5.1 物理验证—DRC&LVS:Calibre率先占据市场

Calibre nmDRC与nmLVS是全定制设计DRC&LVS环节的行业标准工具。优势:Calibre在物理验证环节率先引入了Hierarchy方式,通过提取重复区域,形成无重叠的Hierarchy结构,大幅减少 错误定位时间,在物理验证环节一直保持着较高的市占率。并研发了包括Calibre nmDRC Recon、3DSTACK等适用于 各类场景的检查工具。 劣势:相较于Cadence与Synopsys,Mentor缺乏Virtuoso、Custom Compiler等平台型设计工具,随着设计一致性要求 的不断提高,Calibre的协同性相对弱于其他产品。

3.5.2 物理验证—重要评判因素:对下游工艺的紧密跟踪体现核心能力

物理验证本质上是根据晶圆厂提供的设计要求,对芯片设计结果进行检查。因而与晶圆厂的紧密合作,对下游工艺的紧 密跟踪保证了物理验证工具的核心竞争力。 Cadence、Synopsys以及Mentor均与晶圆厂紧密合作。如Calibre连续多年均获得台积电先进制程的工艺认证。通过 对下游工艺的及时更新,龙头EDA厂商能保证其技术水平始终能够跟进市场最新需求。 随着芯片进程不断压缩,芯片设计与验证的一致性要求也越来越高。拥有全流程解决方案的Cadence与Synopsys相对 Mentor有相对优势。Cadence的Virtuoso作为设计平台能够集成各类自有与第三方的物理验证工具,包括Mentor的 Calibre。

3.5.3 物理验证—国产机会:加强合作紧跟工艺,向数字等方向延展

国产头部厂商具备优势,有望加速实现向数字设计领域的业务外延及市场整合。国产格局:国产厂商中,物理验证环节市场参与者较多,主要产品包括Argus、概伦电子全定制设计平台NanoDesigner 中的ND iDRC/iLVS等。边界拓展:在物理验证环节,全定制设计与数字设计之间底层技术复用程度较高,国产全定制设计EDA中的物理验证工 具或可拓展业务边界,打开更大市场空间。市场整合:当前国产市场中,一方面与全球顶级晶圆厂合作深度仍有待提升,另一方面,也少有EDA厂商拥有全流程的 解决方案能力。因而,短期内,下游工艺要求或尚未对市场形成压力,但在长期内,随着制程工艺进一步升级以及国产 市场逐渐走向饱和,技术与竞争压力将会导致国产市场出现新一轮的整合动作。

以上是关于国产EDA与FPGA芯片验证方案的主要内容,如果未能解决你的问题,请参考以下文章