ESP32Tensilica LX7/NX与ESP32

Posted CodeAllen嵌入式编程

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了ESP32Tensilica LX7/NX与ESP32相关的知识,希望对你有一定的参考价值。

Tensilica 是一个迅速成长的公司,公司主要产品是在专业性应用程序微处理器上,为现今高容量嵌入式系统提供最优良的解决方案。公司成立于1997年7月,该公司的投资者包括三家声名卓著的创投公司:Oak Investment Partners, Worldview Technology Partners 和 Foundation Capital, 与高科技电子业内著名的五家公司:Cisco Systems,Inc,Matsushita Electric Industrial Company Ltd, Altera Corporation,NEC Corporation 和 Conexant Systems。Tensilica的创始人为Chris Rowen,同时也是第一任CEO,他原来曾任职于Intel,Stanford,MIPS,SGI和Synopsys,同时他也是可重构处理思想的提出者和实践者。Tensilica公司创立的目的则是提供一种可以实现可重构的、核基于ASIC的、拥有对应软件开发工具的专用微处理器解决方法。

其HIFI系列产品的主要应用包括:

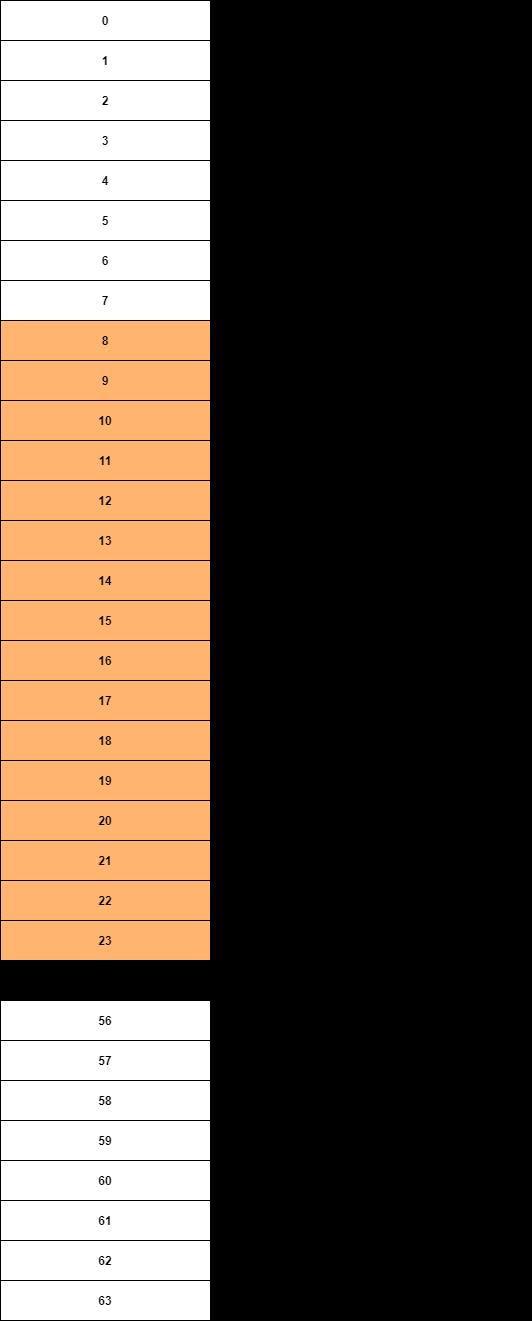

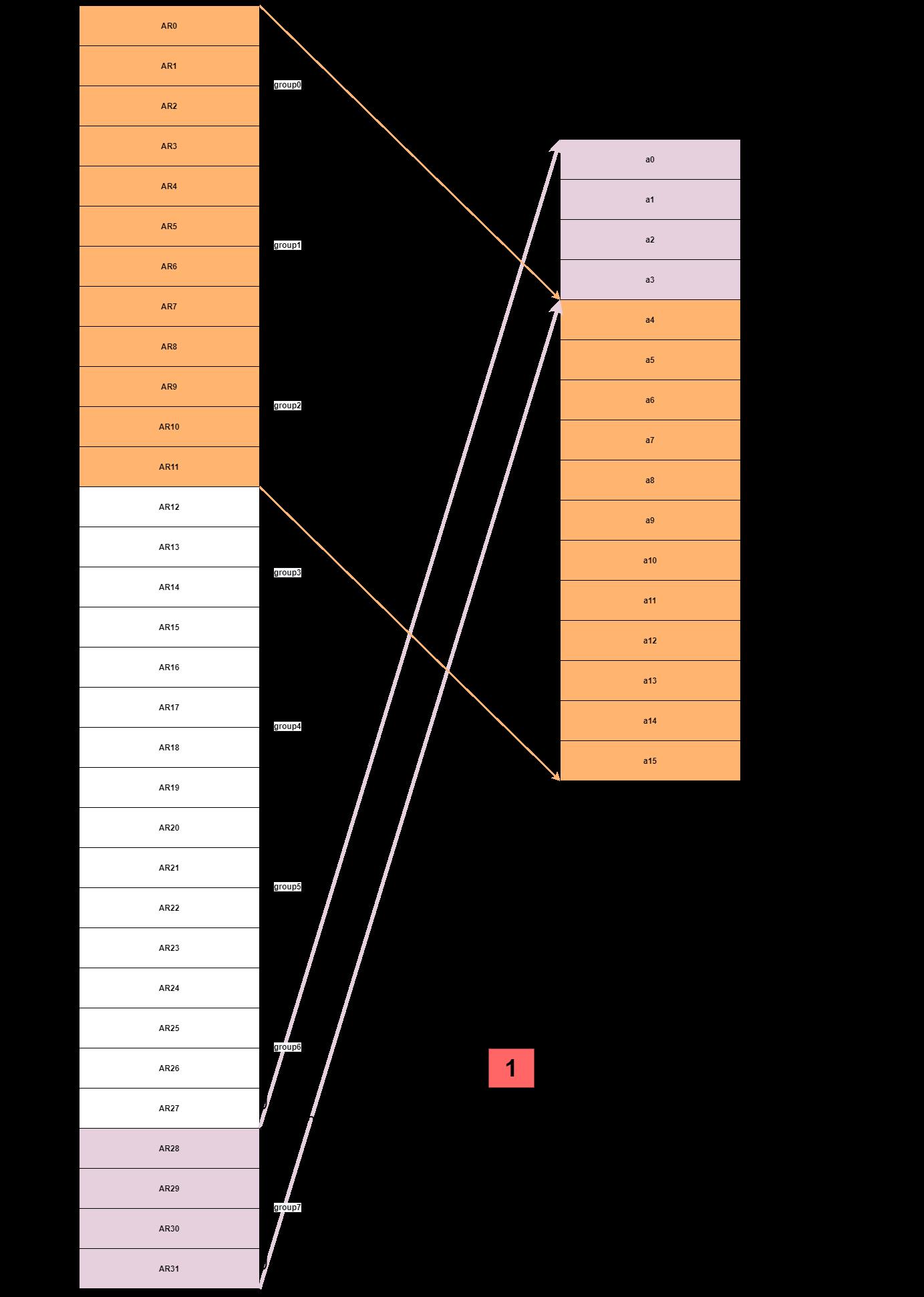

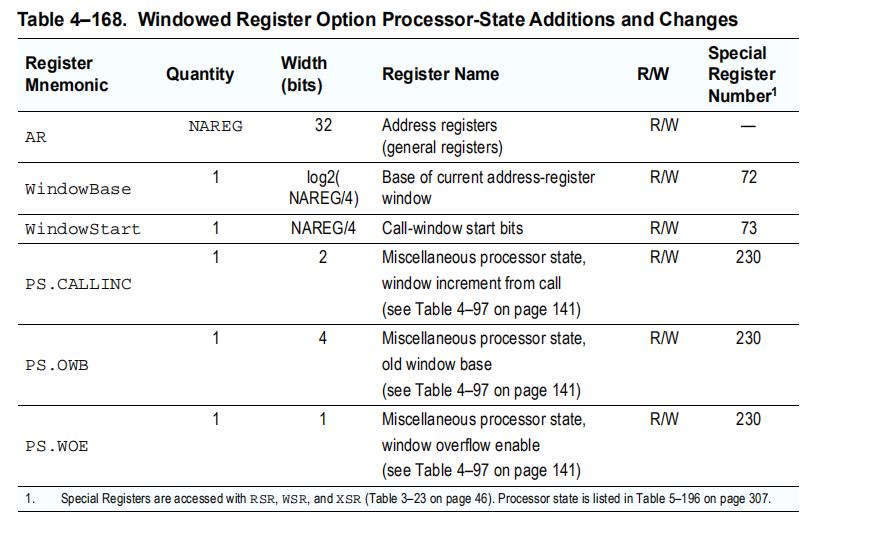

1.寄存器window的概念可以将物理寄存器和逻辑寄存器(ISA寄存器)分离开来,在设计上增加了一层抽象,可以避免在函数调用的时候频繁的压栈和出栈操作,下图展示在64个物理寄存器上实现的寄存器窗口,虽然ISA仅仅定义了16个AR寄存器,但是实际微架构设计时不限物理寄存器的数量的,当然,成本是随着微架构寄存器的数目增加而增加的。

更具体的一个映射的例子:

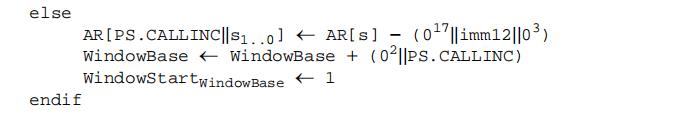

物理寄存器数量是有限的,如果嵌套多层调用call4/8/12,则一定会发生覆盖原来寄存器窗口的情况,覆盖发生时,Xtensa通过寄存器窗口异常来处理这种情况。寄存器窗口机制中,任何地方引用a0-a3都不会产生register window异常,用户在c或者汇编代码里面可以任意使用,因为在任意环境里,当前逻辑窗口的寄存器,要么无覆盖发生,要么已经在call/entry指令中进行了压栈保存。a4-a15的高位寄存器引用会触发低位寄存器的覆盖检测,哪怕没有显示的使用低位寄存器,触发的顺序是先进行overflow4,然后overflow8至overflow12.

entry指令的执行伪码:

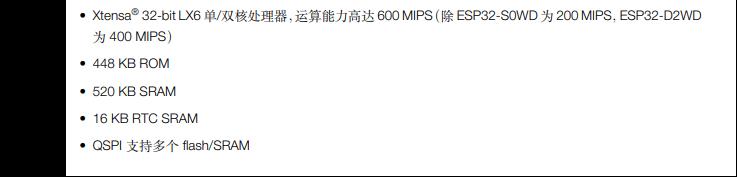

2.ESP32和HIFI3/4/5的区别

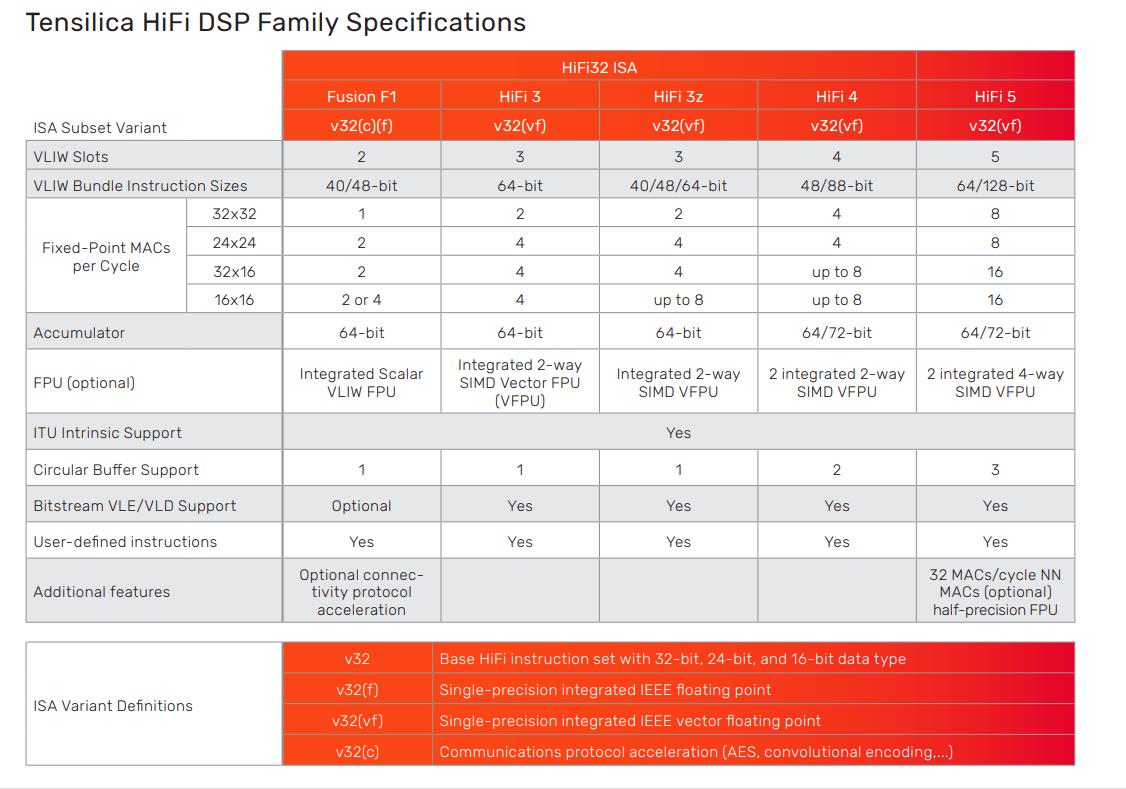

HIFI3/4/5的ISA是一样的,区别可能在于资源的数量。

总结:

- HIFI系列在Xtensa核心的基础上,集成了DSP Extensions,比如集成VLIW计算单元加速各种DSP操作等等,ESP32核心则没有这些扩展。

- ESP32和HIFI系列的base ISA部分应该是一样的,这有点类似于RISCV ISA RV32I/64I extensions的设计。但是,Base ISA相同并不表示处理器的特性是完全一样的,尤其是Xtensa这种支持可重构的处理器设计架构,它非常容易扩展新的指令,所以HIFI系列作为xtensa core的DSP实现,一定在增加了支持fast DSP操作DSP指令。ESP32不是DSP,它没有这些。

- ESP32确实有一些32bit mac单指令,比如单周期的乘累加指令,虽然也可以用它做一些DSP操作,但是这和HIFI核的做法是完全不一样的,HIFI核基于硬件vector和VLIW的方式实现,是面向DSP处理的,性能肯定不在一个水平上。

- 实际上github上有一个项目,就是实现了一个用ESP32进行类似DSP操作的算法库。esp-dsp项目。

- HIFI5 DSP是LX系列处理器的一个configuration option,可以加入在LX系列处理器核里面构成DSP核,没有加入的当然不算是DSP,当使用DSP的扩展配置后,编译器会自动将指令用HIFI5 DSP加速的方式编译。

- HIFI5 DSP is built on the baseline of Xtensa RISC Architecture, 它最厉害的能力来源于DSP指令集和音频指令集扩展,而非baseline ISA,如果想看baseline ISA咋样,可以去用esp32或esp8266体验一下。

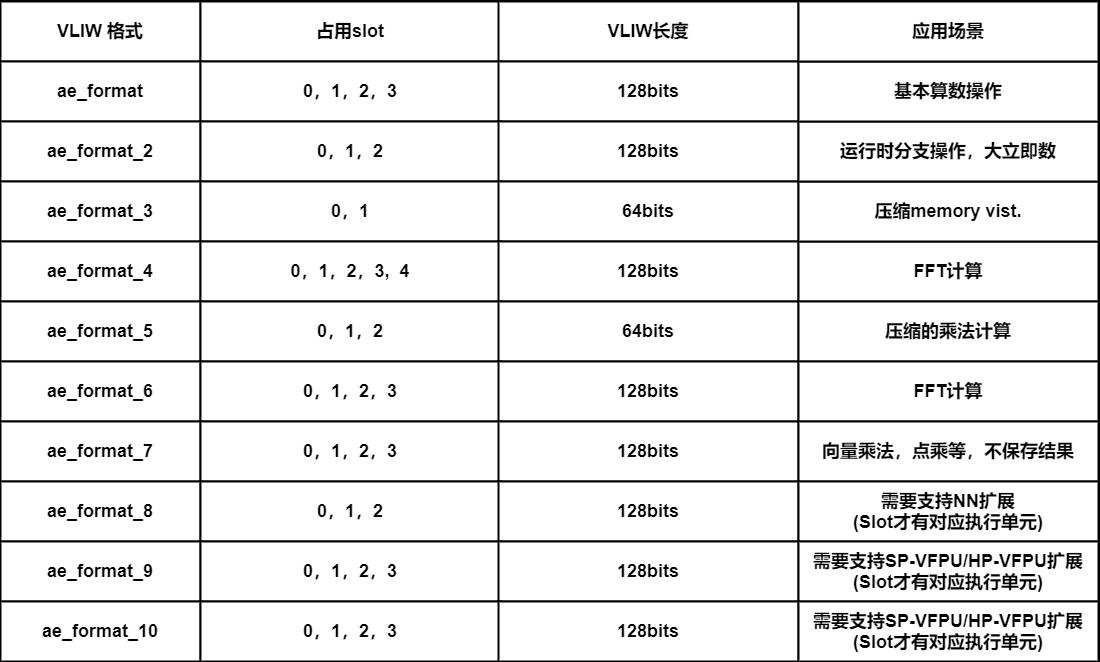

- HIFI系列处理器最多可以同时发射5条指令(没有结构,数据相关),并将这五条指令打包成128位的超长指令,分配给五套slots执行单元去执行。存在结构相关的指令无法在一起打包成VLIW,比如,由于只有 slot0支持load操作,所以无法同时打包两条或者以上的l内存load操作执行,其它依赖slot能力的指令也有限制,具体要看每个slot的支持信息。

- 貌似xtensa对自家编译器xcc的寄存器调度能力非常自信,所以它不推荐用户在HIFI5上手搓DSP汇编

VLIW示意图,slot是执行单元,每个能力不同,需要注意指令不能存在结构相关。

3.根据谷歌到的关于xtensa的资料,提取到的一些关于VLIW应用场景和用法的一些信息,一共包括十种指令打包格式,每种格式在所用资源,应用场景,指令长度方面有所差异。

关于NX可扩展处理器架构需要补充说明。

以上是关于ESP32Tensilica LX7/NX与ESP32的主要内容,如果未能解决你的问题,请参考以下文章