[架构之路-15]:目标系统 - 硬件平台 - 什么是多核设计?多核面临的问题?什么是大小核设计?

Posted 文火冰糖的硅基工坊

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了[架构之路-15]:目标系统 - 硬件平台 - 什么是多核设计?多核面临的问题?什么是大小核设计?相关的知识,希望对你有一定的参考价值。

目录

第1章 什么是多核架构

1.1 什么是单核架构

单核处理器是仅具有单个中央处理单元 (CPU)的计算单元ALU,所有程序或软件仅在一个内核上执行。

多核处理器由两个或多个称为“核心”的处理器组成的计算组件。这些内核以比单核最有效的方式读取和执行程序。

1.2 什么是多核架构

多核处理器技术是CPU设计中的一项先进技术。它把两个以上的处理器核集成在一块芯片上,以增强计算性能。CMP通过在多个CPU核上分配工作负荷,并且依靠到内存和输入输出(I/O)的高速片上互联和高带宽管道对系统性能进行提升。CMP(单芯片多处理器)技术来替代复杂性较高的单线程CPU。

1.3 为什么要多核架构

处理器实际性能是处理器在每个时钟周期内所能处理器指令数的总量,因此增加一个内核,理论上处理器每个时钟周期内可执行的单元数将增加一倍。

原因很简单,因为它可以并行的执行指令,含有几个内核,单位时间可以执行的指令数量上限就会增加几倍。而在芯片内部多嵌入几个内核的难度要远远比加大内核的集成度要简单很多。

于是,多核就能够在不提高生产难度的前提下,用多个低频率核心产生超过高频率单核心的处理效能,特别是服务器产品需要面对大量并行数据,多核心分配任务更能够提高工作效率。

可以看作一种多处理器协作的微缩形式,并且达到更加的性能价格比,一套系统达到多套系统的性能。多核的介入,使得摩尔定律在另一个层面的意义上,避免了尴尬的局面。

随着单核CPU的处理速度的提升, 其发热会大大增加、性价比也会降低。也就是说,单单提升CPU主频这种发展方向已经面临极限,主频越高,能耗越大, 单位面积的发热越大,硬件可靠性越低。

第2章 多核架构的组成

2.1 多核之间通信模型

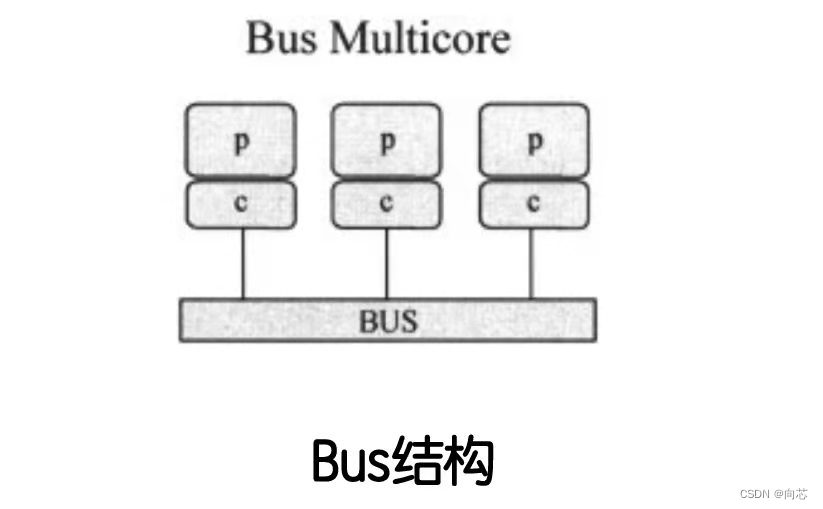

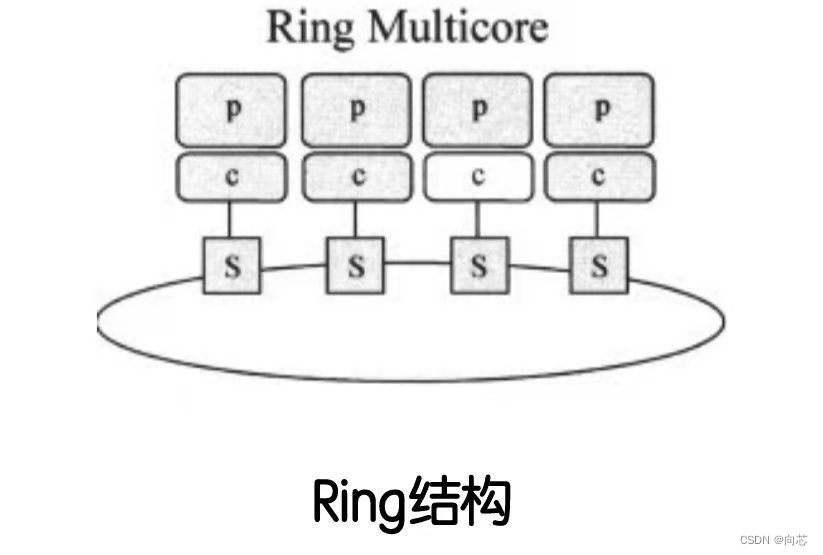

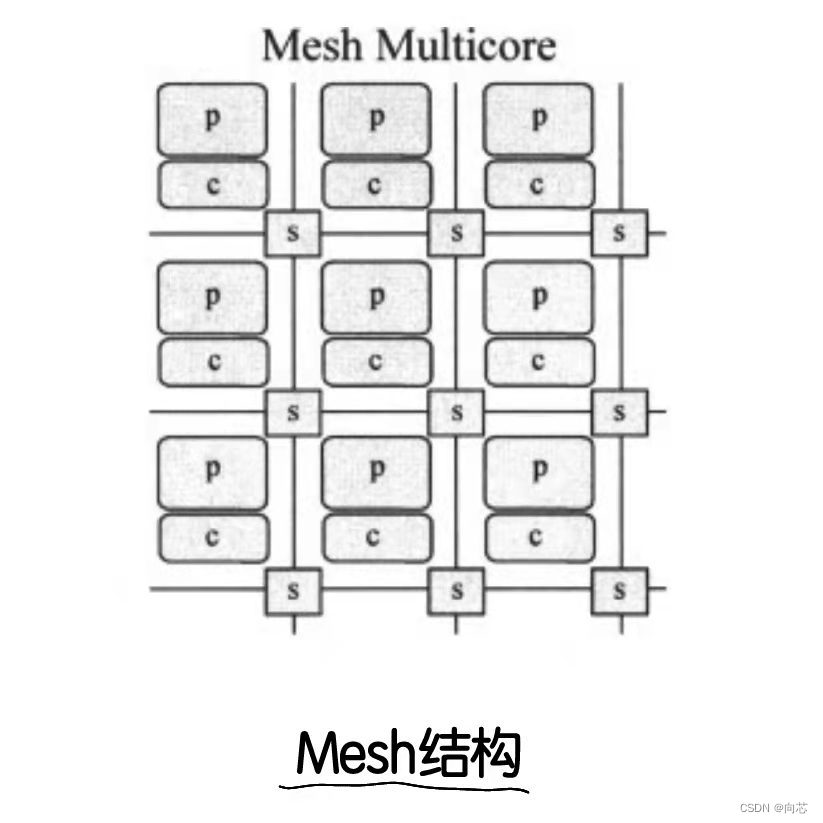

p表示内核, c表示内核拥有的cache,s表示Switch,用于核间的通信。线条表示通信路径。

(1)共享总线Bus结构

Bus结构是比较简单的核间通信方式,内核挂在通信总线上,实现简单,

缺点是每两个内核通信都要占用总线,导致其他的核不能通信,通信效率极低。

(2)交换机Switch结构

Switch结构是通信效率最高的结构,每个内核两两相连,在1和2通信的同时,3和4也可以同时通信。如果核少还好,如果核太多,这种连接方式需要耗费大量的互联资源,通常4个核左右的处理器采用这种方式。

(3)环状Ring结构

Ring结构是介于Bus和Switch之间的一种结构,核1和核3通信需要经过核2,形成一个环,越近的两个核通信效率越高,通信连线并不复杂,实现成本也低。

通常8个核左右采用这种方式,Intel的很多处理器采用这种结构。

(4)网格Mesh结构

Mesh结构适用于核数非常多的情况,类似于二维的Ring结构。

当核数太多时,使用Switch结构会导致连线异常复杂,N个内核两两通信,需要N x N量级数的连线,而Mesh是很好的选择。

Mesh结构简单,易于扩展,通信效率也高。众核处理器(core很多时,多核就变成众核)首选这种方式,如Tilera的64核/100核处理器。

2.2 多核的案例

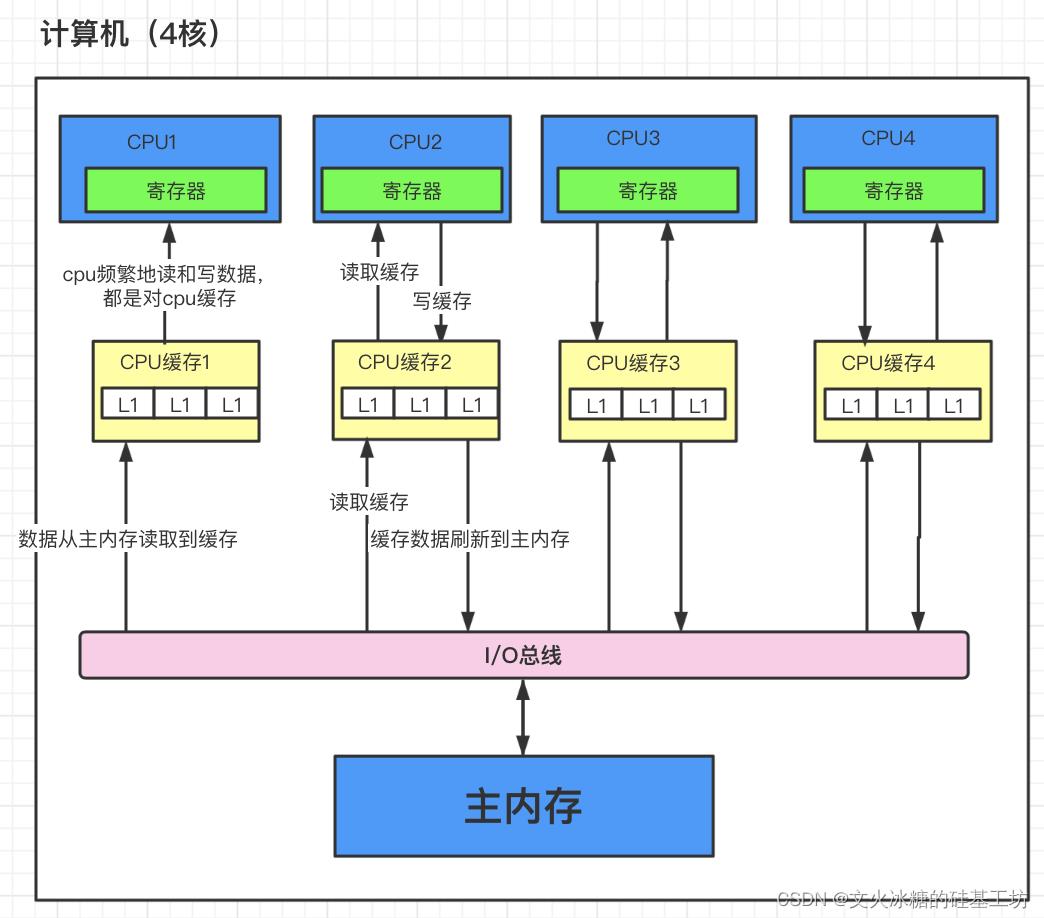

多核CPU就是基板上集成有多个单核CPU。

第3章 多核处理器的挑战

虽然多核能利用集成度提高带来的诸多好处,让芯片的性能成倍地增加,但很明显的是原来系统级的一些问题便引入到了处理器内部。

与单核处理器相比,多核处理器在体系结构、软件、功耗和安全性设计等方面面临着巨大的挑战。

3.1 程序执行问题

处理器设计的首要问题是选择程序执行模型。

程序执行模型的适用性决定多核处理器能否以最低的代价提供最高的性能。程序执行模型是编译器设计人员与系统实现人员之间的接口。编译器设计人员决定如何将一种高级语言程序按一种程序执行模型转换成一种目标机器语言程序; 系统实现人员则决定该程序执行模型在具体目标机器上的有效实现。当目标机器是多核体系结构时,产生的问题是: 多核体系结构如何支持重要的程序执行模型?是否有其他的程序执行模型更适于多核的体系结构?这些程序执行模型能多大程度上满足应用的需要并为用户所接受?

3.2 Cache一致性问题

由于同一份数据在整个系统中存在多份,分布在不同的处理器的cache中,如果一个处理器修改了自己的那份数据,则其它处理器的数据就不是最新有效的了。如果保证核间的cache一致性是多核处理器设计的一个重要方面。

在传统多处理器系统结构中广泛采用的Cache一致性模型有: 顺序一致性模型、弱一致性模型、释放一致性模型等。与之相关的Cache一致性机制主要有总线的侦听协议和基于目录的目录协议。CMP系统大多采用基于总线的侦听协议。

3.3 核间互联

多核之间通过共享内存通信是通过往全局内存中写入数据和读取数据来完成的,当多个处理器同时访问(写入或者读取)共享内存时会导致总线上的竞争,从而导致系统性能恶化,所以优化总线结构设计也是提升多核性能的一个关键技术。

基于片上互连的结构是指每个CPU核心具有独立的处理单元和Cache,各个CPU核心通过交叉开关或片上网络等方式连接在一起。各个CPU核心间通过消息通信。这种结构的优点是可扩展性好,数据带宽有保证; 缺点是硬件结构复杂,且软件改动较大。

3.4 总线设计

传统微处理器中,Cache不命中或访存事件都会对CPU的执行效率产生负面影响,而总线接口单元(BIU)的工作效率会决定此影响的程度。当多个CPU核心同时要求访问内存或多个CPU核心内私有Cache同时出现Cache不命中事件时,BIU对这多个访问请求的仲裁机制以及对外存储访问的转换机制的效率决定了CMP系统的整体性能。因此寻找高效的多端口总线接口单元(BIU)结构,将多核心对主存的单字访问转为更为高效的猝发(burst)访问; 同时寻找对CMP处理器整体效率最佳的一次Burst访问字的数量模型以及高效多端口BIU访问的仲裁机制将是CMP处理器研究的重要内容,Inter推出了最新的英特尔智能互连技术(QPI)技术总线,更大程度发掘了多核处理器的实力 。

3.5 操作系统设计

任务调度、中断处理、同步互斥

对于多核CPU,优化操作系统任务调度算法是保证效率的关键。

一般任务调度算法有全局队列调度和局部队列调度。

前者是指操作系统维护一个全局的任务等待队列,当系统中有一个CPU核心空闲时,操作系统就从全局任务等待队列中选取就绪任务开始在此核心上执行。这种方法的优点是CPU核心利用率较高。

后者是指操作系统为每个CPU内核维护一个局部的任务等待队列,当系统中有一个CPU内核空闲时,便从该核心的任务等待队列中选取恰当的任务执行,这种方法的优点是任务基本上无需在多个CPU核心间切换,有利于提高CPU核心局部Cache命中率。

多数多核CPU操作系统采用的是基于全局队列的任务调度算法。

多核的中断处理和单核有很大不同。多核的各处理器之间需要通过中断方式进行通信,所以多个处理器之间的本地中断控制器和负责仲裁各核之间中断分配的全局中断控制器也需要封装在芯片内部。

另外,多核CPU是一个多任务系统。由于不同任务会竞争共享资源,因此需要系统提供同步与互斥机制。

而传统的用于单核的解决机制并不能满足多核,需要利用硬件提供的“读-修改-写”的原子操作或其他同步互斥机制来保证。

3.6 低功耗设计

半导体工艺的迅速发展使微处理器的集成度越来越高,同时处理器表面温度也变得越来越高并呈指数级增长,每三年处理器的功耗密度就能翻一番。低功耗和热优化设计已经成为微处理器研究中的核心问题。CMP的多核心结构决定了其相关的功耗研究是一个至关重要的课题。

低功耗设计是一个多层次问题,需要同时在操作系统级、算法级、结构级、电路级等多个层次上进行研究。每个层次的低功耗设计方法实现的效果不同——抽象层次越高,功耗和温度降低的效果越明显。

3.7 存储器墙

为了使芯片内核充分地工作,最起码的要求是芯片能提供与芯片性能相匹配的存储器带宽,虽然内部Cache的容量能解决一些问题,但随着性能的进一步提高,必须有其他一些手段来提高存储器接口的带宽,如增加单个管脚带宽的DDR、DDR2、QDR、XDR等。同样,系统也必须有能提供高带宽的存储器。所以,芯片对封装的要求也越来越高,虽然封装的管脚数每年以20%的数目提升,但还不能完全解决问题,而且还带来了成本提高的问题,为此,怎样提供一个高带宽,低延迟的接口带宽,是必须解决的一个重要问题。

3.8 可靠性及安全性设计

随着技术革新的发展,处理器的应用渗透到现代社会的各个层面,但是在安全性方面却存在着很大的隐患。一方面,处理器结构自身的可靠性低下,由于超微细化与时钟设计的高速化、低电源电压化,设计上的安全系数越来越难以保证,故障的发生率逐渐走高。另一方面,来自第三方的恶意攻击越来越多,手段越来越先进,已成为具有普遍性的社会问题。可靠性与安全性的提高在计算机体系结构研究领域备受注目。

今后,CMP这类处理器芯片内有多个进程同时执行的结构将成为主流,再加上硬件复杂性、设计时的失误增加,使得处理器芯片内部也未必是安全的,因此,安全与可靠性设计任重而道远。

3.9 同构还是异构

CMP的构成分成同构和异构两类,同构是指内部核的结构是相同的,而异构是指内部的核结构是不同的。为此,面对不同的应用研究核结构的实现对未来微处理器的性能至关重要。核本身的结构,关系到整个芯片的面积、功耗和性能。怎样继承和发展传统处理器的成果,直接影响多核的性能和实现周期。同时,根据Amdahl定理,程序的加速比决定于串行部分的性能,所以,从理论上来看似乎异构微处理器的结构具有更好的性能。核所用的指令系统对系统的实现也是很重要的,多核之间采用相同的指令系统还是不同的指令系统,能否运行操作系统等。异构的和核结构称为大小核架构。

第4章 大小核架构

众所周知,自从PC处理器步入多核心时代之后,很长一段时间里,“更多核心、更高频率”都被认为是提高处理器性能表现的金科玉律。但随着主流价位段上的CPU从双核来到四核,又从四核来到六核;随着“家用高端”的标准从过去的四核、八核,现在逐渐变成十核(i9-10900K)和十六核(Ryzen9 3950X),多核心处理器的成本、发热和功耗如今已经变成了不容忽视的严峻问题。

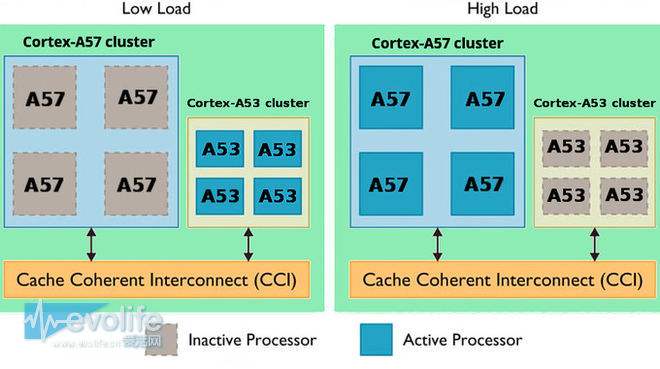

“大小核(Big-Little)”设计通过将多个高性能、高成本、高发热的大核心,与多个低功耗、低成本、低发热的小核心相互组合,按需调度的方式(是实现大小核高效的核心),成功地兼顾了现代智能手机所需的峰值性能以及日常省电表现。

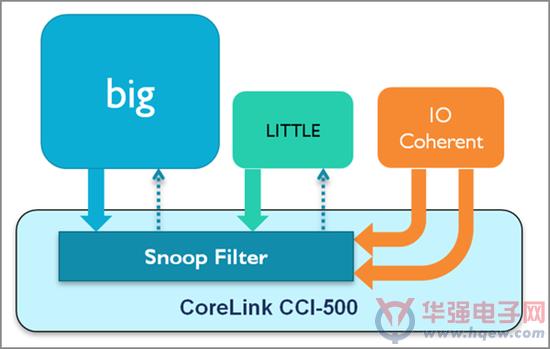

ARM的第一个big.LITTLE系统设计中,一个`big`的ARM Cortex-A15处理器与一个`LITTLE`的ARM Cortex-A7处理器配合使用,构建起一个既能够完成高强度任务,同时具有不错的效能的系统。实际运用中,ARM Cortex-A15和ARM Cortex-A7处理器通过CoreLink CCI-400内部总线进行连接,组成一个足以面对各种运用场景的灵活系统。使同一应用程序软件在二者之间无缝切换。通过为每个任务选择最佳处理器,big.LITTLE 可以使电池的使用寿命延长高达 70%。

进步了解:多芯片互联技术

[从零开始学习FPGA编程-57]:视野篇-异构系统、异构芯片、大小核、芯片互联网、UCIe标准_文火冰糖的硅基工坊的博客-CSDN博客

以上是关于[架构之路-15]:目标系统 - 硬件平台 - 什么是多核设计?多核面临的问题?什么是大小核设计?的主要内容,如果未能解决你的问题,请参考以下文章