门电路工作原理?

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了门电路工作原理?相关的知识,希望对你有一定的参考价值。

门电路是数字电路的基本组成单元。它有一个或多个输入端和一个输出端,输入和输出为低电平和高电平(分别代表2进制0和1)。

门电路一般有:与门、或门、非门、与非门、或非门等。各种门电路有着不同的功能,即针对不同的输入数值给出输出数值(比如或门要求两个输入值中有一个或以上为1时输出1;与门在两个输入值都为1是输出1,否则输出0;非门只有一个输入,而输出与输入反相),就像数学上简单的方程式;不同种类的门就像不同的方程式;大量的各种门可以描述更为复杂的方程式。

可不可以给我详细一点介绍这些门电路的工作原理?

希望能够与电脑主板有点联系。谢谢!!!

http://www.fjtu.com.cn/fjnu/courseware/0321/course/_source/web/lesson/char2/j6.htm 看看把

CMOS逻辑门电路是在TTL电路问世之后 ,所开发出的第二种广泛应用的数字集成器件,从发展趋势来看,由于制造工艺的改进,CMOS电路的性能有可能超越TTL而成为占主导地位的逻辑器件 。CMOS电路的工作速度可与TTL相比较,而它的功耗和抗干扰能力则远优于TTL。此外,几乎所有的超大规模存储器件 ,以及PLD器件都采用CMOS艺制造,且费用较低。

早期生产的CMOS门电路为4000系列 ,随后发展为4000B系列。当前与TTL兼容的CMO器件如74HCT系列等可与TTL器件交换使用。下面首先讨论CMOS反相器,然后介绍其他CMO逻辑门电路。

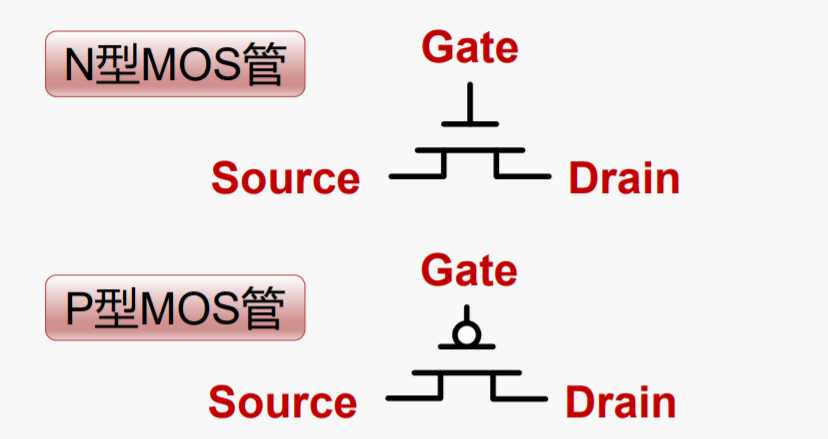

MOS管结构图

MOS管主要参数:

1.开启电压VT

·开启电压(又称阈值电压):使得源极S和漏极D之间开始形成导电沟道所需的栅极电压;

·标准的N沟道MOS管,VT约为3~6V;

·通过工艺上的改进,可以使MOS管的VT值降到2~3V。

2. 直流输入电阻RGS

·即在栅源极之间加的电压与栅极电流之比

·这一特性有时以流过栅极的栅流表示

·MOS管的RGS可以很容易地超过1010Ω。

3. 漏源击穿电压BVDS

·在VGS=0(增强型)的条件下 ,在增加漏源电压过程中使ID开始剧增时的VDS称为漏源击穿电压BVDS

·ID剧增的原因有下列两个方面:

(1)漏极附近耗尽层的雪崩击穿

(2)漏源极间的穿通击穿

·有些MOS管中,其沟道长度较短,不断增加VDS会使漏区的耗尽层一直扩展到源区,使沟道长度为零,即产生漏源间的穿通,穿通后

,源区中的多数载流子,将直接受耗尽层电场的吸引,到达漏区,产生大的ID

4. 栅源击穿电压BVGS

·在增加栅源电压过程中,使栅极电流IG由零开始剧增时的VGS,称为栅源击穿电压BVGS。

5. 低频跨导gm

·在VDS为某一固定数值的条件下 ,漏极电流的微变量和引起这个变化的栅源电压微变量之比称为跨导

·gm反映了栅源电压对漏极电流的控制能力

·是表征MOS管放大能力的一个重要参数

·一般在十分之几至几mA/V的范围内

6. 导通电阻RON

·导通电阻RON说明了VDS对ID的影响 ,是漏极特性某一点切线的斜率的倒数

·在饱和区,ID几乎不随VDS改变,RON的数值很大 ,一般在几十千欧到几百千欧之间

·由于在数字电路中 ,MOS管导通时经常工作在VDS=0的状态下,所以这时的导通电阻RON可用原点的RON来近似

·对一般的MOS管而言,RON的数值在几百欧以内

7. 极间电容

·三个电极之间都存在着极间电容:栅源电容CGS 、栅漏电容CGD和漏源电容CDS

·CGS和CGD约为1~3pF

·CDS约在0.1~1pF之间

8. 低频噪声系数NF

·噪声是由管子内部载流子运动的不规则性所引起的

·由于它的存在,就使一个放大器即便在没有信号输人时,在输 出端也出现不规则的电压或电流变化

·噪声性能的大小通常用噪声系数NF来表示,它的单位为分贝(dB)

·这个数值越小,代表管子所产生的噪声越小

·低频噪声系数是在低频范围内测出的噪声系数

·场效应管的噪声系数约为几个分贝,它比双极性三极管的要小

一、CMOS反相器

由本书模拟部分已知,MOSFET有P沟道和N沟道两种,每种中又有耗尽型和增强型两类。由N沟道和P沟道两种MOSFET组成的电路称为互补MOS或CMOS电路。

下图表示CMOS反相器电路,由两只增强型MOSFET组成,其中一个为N沟道结构,另一个为P沟道结构。为了电路能正常工作,要求电源电压VDD大于两个管子的开启电压的绝对值之和,即

VDD>(VTN+|VTP|) 。

1.工作原理

首先考虑两种极限情况:当vI处于逻辑0时 ,相应的电压近似为0V;而当vI处于逻辑1时,相应的电压近似为VDD。假设在两种情况下N沟道管 TN为工作管P沟道管TP为负载管。但是,由于电路是互补对称的,这种假设可以是任意的,相反的情况亦将导致相同的结果。

下图分析了当vI=VDD时的工作情况。在TN的输出特性iD—vDS(vGSN=VDD)(注意vDSN=vO)上 ,叠加一条负载线,它是负载管TP在 vSGP=0V时的输出特性iD-vSD。由于vSGP<VT(VTN=|VTP|=VT),负载曲线几乎是一条与横轴重合的水平线。两条曲线的交点即工作点。显然,这时的输出电压vOL≈0V(典型值<10mV ,而通过两管的电流接近于零。这就是说,电路的功耗很小(微瓦量级)

下图分析了另一种极限情况,此时对应于vI=0V。此时工作管TN在vGSN=0的情况下运用,其输出特性iD-vDS几乎与横轴重合 ,负载曲线是负载管TP在vsGP=VDD时的输出特性iD-vDS。由图可知,工作点决定了VO=VOH≈VDD;通过两器件的电流接近零值 。可见上述两种极限情况下的功耗都很低。

由此可知,基本CMOS反相器近似于一理想的逻辑单元,其输出电压接近于零或+VDD,而功耗几乎为零。

2.传输特性

下图为CMOS反相器的传输特性图。图中VDD=10V,VTN=|VTP|=VT=

2V。由于 VDD>(VTN+|VTP|),因此,当VDD-|VTP|>vI>VTN 时,TN和TP两管同时导通。考虑到电路是互补对称的,一器件可将另一器件视为它的漏极负载。还应注意到,器件在放大区(饱和区)呈现恒流特性,两器件之一可当作高阻值的负载。因此,在过渡区域,传输特性变化比较急剧。两管在VI=VDD/2处转换状态。

3.工作速度

CMOS反相器在电容负载情况下,它的开通时间与关闭时间是相等的,这是因为电路具有互补对称的性质。下图表示当vI=0V时 ,TN截止,TP导通,由VDD通过TP向负载电容CL充电的情况。由于CMOS反相器中,两管的gm值均设计得较大,其导通电阻较小,充电回路的时间常数较小。类似地,亦可分析电容CL的放电过程。CMOS反相器的平均传输延迟时间约为10ns。

二、CMOS门电路

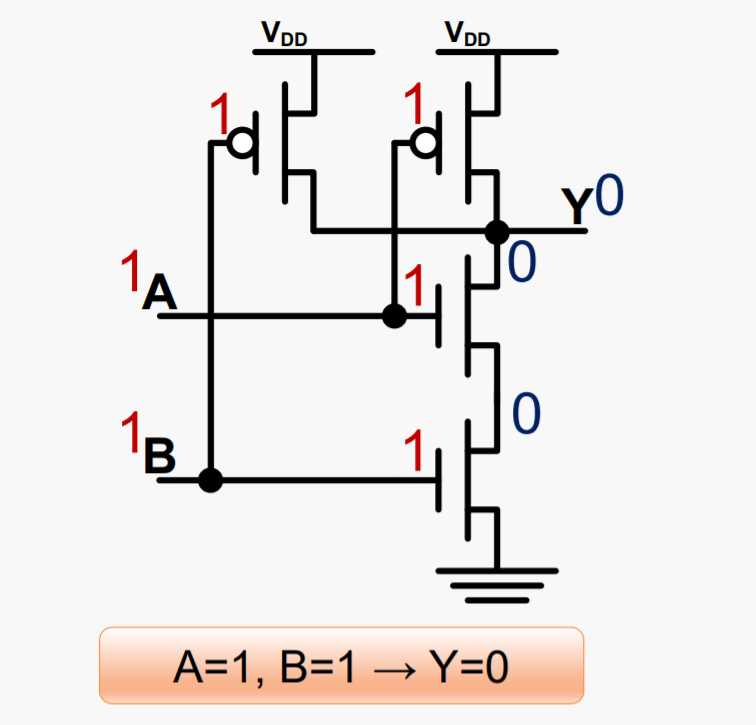

1.与非门电路

下图是2输入端CMOS与非门电路,其中包括两个串联的N沟道增强型MOS管和两个并联的P沟道增强型MOS管。每个输入端连到一个N沟道和一个P沟道MOS管的栅极。当输入端A、B中只要有一个为低电平时,就会使与它相连的NMOS管截止,与它相连的PMOS管导通,输出为高电平;仅当A、B全为高电平时,才会使两个串联的NMOS管都导通,使两个并联的PMOS管都截止,输出为低电平。

因此,这种电路具有与非的逻辑功能,即

n个输入端的与非门必须有n个NMOS管串联和n个PMOS管并联。

2.或非门电路

下图是2输入端CMOS或非门电路。其中包括两个并联的N沟道增强型MOS管和两个串联的P沟道增强型MOS管。

当输入端A、B中只要有一个为高电平时,就会使与它相连的NMOS管导通,与它相连的PMOS管截止,输出为低电平;仅当A、B全为低电平时,两个并联NMOS管都截止,两个串联的PMOS管都导通,输出为高电平。

因此,这种电路具有或非的逻辑功能,其逻辑表达式为

显然,n个输入端的或非门必须有n个NMOS管并联和n个PMOS管并联。

比较CMOS与非门和或非门可知,与非门的工作管是彼此串联的,其输出电压随管子个数的增加而增加;或非门则相反,工作管彼此并联,对输出电压不致有明显的影响。因而或非门用得较多。

3.异或门电路

上图为CMOS异或门电路。它由一级或非门和一级与或非门组成。或非门的输出。而与或非门的输出L即为输入A、B的异或

如在异或门的后面增加一级反相器就构成异或非门,由于具有的功能,因而称为同或门。异成门和同或门的逻辑符号如下图所示。

三、BiCMOS门电路

双极型CMOS或BiCMOS的特点在于,利用了双极型器件的速度快和MOSFET的功耗低两方面的优势,因而这种逻辑门电路受到用户的重视

。

1.BiCMOS反相器

上图表示基本的BiCMOS反相器电路,为了清楚起见,MOSFET用符号M表示BJT用T表示。T1和T2构成推拉式输出级。而Mp、MN、M1、M2所组成的输入级与基本的CMOS反相器很相似。输入信号vI同时作用于MP和MN的栅极。当vI为高电压时MN导通而MP截止;而当vI为低电压时,情况则相反,Mp导通,MN截止。当输出端接有同类BiCMOS门电路时,输出级能提供足够大的电流为电容性负载充电。同理,已充电的电容负载也能迅速地通过T2放电。

上述电路中T1和T2的基区存储电荷亦可通过M1和M2释放,以加快

电路的开关速度。当vI为高电压时M1导通,T1基区的存储电荷迅速消散。这种作用与TTL门电路的输入级中T1类似。同理 ,当vI为低电压时,电源电压VDD通过MP以激励M2使M2导通,显然T2基区的存储电荷通过M2而消散。可见,门电路的开关速度可得到改善。

2.BiCMOS门电路

根据前述的CMOS门电路的结构和工作原理,同样可以用BiCMOS技术实现或非门和与非门。如果要实现或非逻辑关系,输入信号用来驱动并联的N沟道MOSFET,而P沟道MOSFET则彼此串联。正如下图所示的

2输入端或非门。

当A和B均为低电平时,则两个MOSFET MPA和MPB均导通,T1导通而MNA和MNB均截止,输出L为高电平。与此同时,M1通过MPA和MpB被VDD所激励,从而为T2的基区存储电荷提供一条释放通路。

另一方面,当两输入端A和B中之一为高电平时 ,则MpA和MpB的通路被断开,并且MNA或MNB导通,将使输出端为低电平。同时,M1A或M1B为T1的基极存储电荷提供一条释放道路。因此 ,只要有一个输入端接高电平,输出即为低电平。

四、CMOS传输门

MOSFET的输出特性在原点附近呈线性对称关系,因而它们常用作模拟开关。模拟开关广泛地用于取样——保持电路、斩波电路、模数和数模转换电路等。下面着重介绍CMOS传输门。

所谓传输门(TG)就是一种传输模拟信号的模拟开关。CMOS传输门由一个P沟道和一个N沟道增强型MOSFET并联而成,如上图所示。TP和TN是结构对称的器件,它们的漏极和源极是可互换的。设它们的开启电压|VT|=2V且输入模拟信号的变化范围为-5V到+5V 。为使衬底与漏源极之间的PN结任何时刻都不致正偏 ,故TP的衬底接+5V电压,而TN的衬底接-5V电压 。两管的栅极由互补的信号电压(+5V和-5V)来控制,分别用C和表示。

传输门的工作情况如下:当C端接低电压-5V时TN的栅压即为-5V,vI取-5V到+5V范围内的任意值时,TN均不导通。同时,TP的栅压为+5V

,TP亦不导通。可见,当C端接低电压时,开关是断开的。

为使开关接通,可将C端接高电压+5V。此时TN的栅压为+5V ,vI在-5V到+3V的范围内,TN导通。同时TP的棚压为-5V ,vI在-3V到+5V的范围内TP将导通。

由上分析可知,当vI<-3V时,仅有TN导通,而当vI>+3V时,仅有TP导通当vI在-3V到+3V的范围内,TN和TP两管均导通。进一步分析

还可看到,一管导通的程度愈深,另一管的导通程度则相应地减小。换句话说,当一管的导通电阻减小,则另一管的导通电阻就增加。由于两管系并联运行,可近似地认为开关的导通电阻近似为一常数。这是CMOS传输出门的优点。

在正常工作时,模拟开关的导通电阻值约为数百欧,当它与输入阻抗为兆欧级的运放串接时,可以忽略不计。

CMOS传输门除了作为传输模拟信号的开关之外,也可作为各种逻辑电路的基本单元电路。 参考技术A 形象的解释:门,干嘛的?开、关。

那么门电路要完成的就是开关动作,举个例子:你发个信号给某个电路,这个电路就让某个灯开了,再发个信号,就关了。

电路:基本电路可以用三极管来解释,三极管工作有三个状态,放大状态(信号放大)、饱和状态(三极管被导通,相当于开门)、截止状态(三极管被截止,相当于关门)。如果给三极管基极一个足够的电流(假设电平1),那么NPN三极管将会饱和导通,集电极和发射极近视短路,呢么就完成了开的动作(开关作用)(假设电平0),如果将NPN三极管的基极接地,那么三极管就截止,集电极和发射极就近视开路,呢么就完成了关的动作-------这是门电路的最基本的电路

---接着,让1代表开,0代表关,好吧,你要知道非门,与门,或门。。。。的定义以及二进制的换算才行:与门是相反的意思(上面三极管输入1,输出0)。。这是逻辑门电路,上面说的是单纯的门电路。

----逻辑门电路就是你输入一个信号(原因),电路根据设定进行输出(结果) 参考技术B CMOS看,由于制造工艺的改进,CMOS电路的性能有可能超越TTL而成为占主导地位的逻辑器件 。CMOS电路的工作速度可与TTL相比较,而它的功耗和抗干扰能力则远优于TTL。此外,几乎所有的超大规模存储器件 ,以及PLD器件都采用CMOS艺制造,且费用较低。

早期生产的CMOS门电路为4000系列 ,随后发展为4000B系列。当前与TTL兼容的CMO器件如74HCT系列等可与TTL器件交换使用。下面首先讨论CMOS反相器,然后介绍其他CMO逻辑门电路。

MOS管结构图

MOS管主要参数:

1.开启电压VT

·开启电压(又称阈值电压):使得源极S和漏极D之间开始形成导电沟道所需的栅极电压;

·标准的N沟道MOS管,VT约为3~6V;

·通过工艺上的改进,可以使MOS管的VT值降到2~3V。

2. 直流输入电阻RGS

·即在栅源极之间加的电压与栅极电流之比

·这一特性有时以流过栅极的栅流表示

·MOS管的RGS可以很容易地超过1010Ω。

3. 漏源击穿电压BVDS

·在VGS=0(增强型)的条件下 ,在增加漏源电压过程中使ID开始剧增时的VDS称为漏源击穿电压BVDS 参考技术C 不强你的分!

计算机组成与设计—— 门电路的基本原理

集体管

现在集成电路中常使用MOS集体管:Metal-Oxide-Semiconductor(金属-氧化物-半导体)

晶体管有两种类型:N型和P型,由NMOS和PMOS共同构成的互补型MOS集成电路(CMOS)

它们两者的区别在于:NMOS是高电平有效,PMOS是低电平有效。

例如,对NMOS来说,当Gate连接高电平时这个晶体管导通,Source能传到Drain;Gate连接低电平时不导通。

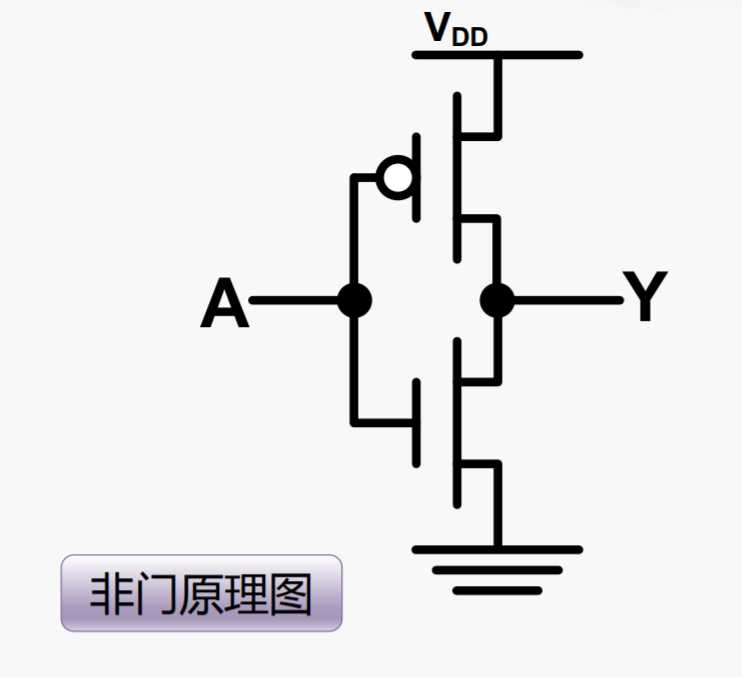

非门

非门可以由NMOS和PMOS组合设计出来,原理图如下:

原理:NMOS和PMOS互补,设A=0,对上面PMOS来说是导通的,VDD能传递到Y,Y = 1,与此同时,对下面NMOS来说是不导通的,地0不会传递到Y,综合得Y=1。A=1同理。

与门

由于与非门得实现比与门简单,所以实际上用非门+与非门——>与门,原理图如下:

原理:设A=B=1,与地相连得两个晶体管是NMOS,所以导通,地0传到Y使得Y=0,与此同时,与Vcc相连得晶体管都是PMOS,所以都不导通,所以1不会传到Y,综上,Y=0.剩下3种情况类似.

或门、异或门等其它得门电路都可以用CMOS构成,这里不细讲了(话说数字逻辑书上都有)。

参考链接:https://www.coursera.org/learn/jisuanji-zucheng/lecture/vc1XB/302-men-dian-lu-de-ji-ben-yuan-li

以上是关于门电路工作原理?的主要内容,如果未能解决你的问题,请参考以下文章