用VHDL写一个有七位(每个5bits)输入,三位控制信号的选择器。

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了用VHDL写一个有七位(每个5bits)输入,三位控制信号的选择器。相关的知识,希望对你有一定的参考价值。

老师要求必须用两种方式写出 behavior的方法很简单,几个case就搞定了。

关键现在的难点在于必须用structure来写出architecture。

我现在的思路是

定义7个输入位ABCDEFG,三位的选择输入端S0、S1、S2.一个 5位输出端OK1=A与(S0非S1非S2非)K2=B与(S0非S1非S2)K3=C与(S0非S1S2非)K4=D与(S0非S1S2)K5=E与(S0S1非S2非)K6=F与(S0S1非S2)K7=G与(S0S1S2非)O=K1或K2或K3或K4或K5或K6或K7这样子的方法有几个问题,第一个如果输入信号是1bit的话我这个是成立的但是我现在是5bits,这时候我就需要用到A1A2A3A4A5B1B2B3B3B4B5。。。。O1O2O3O4O5每个都需要进行上述的逻辑运算。这样的话我的entity部分的定义就很复杂了。再者如果这个成立,我的behavior和structure就不能共用一个testbench了。

----Date: 2013-09-25-

----Author: Mabs

-----------------------------------------------------------------------------------

-------与门------------------------------------------------------------------------

library ieee;

use ieee.std_logic_1164.all;

entity and_ab is

port(

A,B : in std_logic;

C : out std_logic

);

architecture bhv of and_ab is

begin

C <= B and A;

end bhv;

-----------------------------------------------------------------------------------

-------或门------------------------------------------------------------------------

library ieee;

use ieee.std_logic_1164.all;

entity or_ab is

port(

A,B : in std_logic;

C : out std_logic

);

architecture bhv of or_ab is

begin

C <= B or A;

end bhv;

-----------------------------------------------------------------------------------

-------非门------------------------------------------------------------------------

library ieee;

use ieee.std_logic_1164.all;

entity not_a is

port(

A : in std_logic;

C : out std_logic

);

architecture bhv of not_a is

begin

C <= not A;

end bhv;

-----------------------------------------------------------------------------------

-------3input与门------------------------------------------------------------------------

library ieee;

use ieee.std_logic_1164.all;

entity and3_abc is

port(

A,B,C : in std_logic;

D : out std_logic

);

architecture bhv of and3_abc is

component and_ab is

port(

A,B : in std_logic;

C : out std_logic

);

end component;

signal tmp : std_logic;

begin

u1_and: and_ab

port map

( A => A,

B => B,

C => tmp

);

u2_and: and_ab

port map

( A => C,

B => tmp,

C => D

);

end bhv;

-----------------------------------------------------------------------------------

-------7input或门------------------------------------------------------------------------

library ieee;

use ieee.std_logic_1164.all;

entity or7_abc is

port(

A,B,C,D,E,F,G : in std_logic;

H : out std_logic

);

architecture bhv of or7_abc is

component or_ab is

port(

A,B : in std_logic;

C : out std_logic

);

end component;

signal tmpAB,tmpABC,tmpABCD,tmpABCDE,tmpABCDEF : std_logic;

begin

u1_or: or_ab

port map

( A => A,

B => B,

C => tmpAB

);

u2_or: or_ab

port map

( A => C,

B => tmpAB,

C => tmpABC

);

u3_or: or_ab

port map

( A => D,

B => tmpABC,

C => tmpABCD

);

u4_or: or_ab

port map

( A => E,

B => tmpABCD,

C => tmpABCDE

);

u5_or: or_ab

port map

( A => F,

B => tmpABCDE,

C => tmpABCCDEF

);

u6_or: or_ab

port map

( A => G,

B => tmpABCDEF,

C => H

);

end bhv;

-----------------------------------------------------------------------------------

----main-------------------------------------------------------------------------------

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

use ieee.std_logic_arith.all;

use work.pkg;

entity 7sel_to1 is

port(

Din1,Din2,Din3,Din4,Din5,Din6,Din7 : in std_logic_vector(4 downto 0);

S1,S2,S3 : in std_logic;

Dout : out std_logic_vector(4 downto 0)

);

architecture bhv of 7sel_to1 is

component and_ab is

port(

A,B : in std_logic;

C : out std_logic

);

end component;

component or_ab is

port(

A,B : in std_logic;

C : out std_logic

);

end component;

component not_a is

port(

A : in std_logic;

C : out std_logic

);

end component;

component and3_abc is

port(

A,B,C : in std_logic;

D : out std_logic

);

end component;

component or7_abc is

port(

A,B,C,D,E,F,G : in std_logic;

H : out std_logic

);

signal tmp1,tmp2,tmp3,tmp4,tmp5,tmp6,tmp7 : std_logic_vector(4 downto 0);

signal nS1,nS2,nS3 : std_logic;

signal sel1,sel2,sel3,sel4,sel5,sel6,sel7 : std_logic;

begin

---not--------------

u1_not_S1: not_a

port map(

A=>S1,

C=>nS1

);

u2_not_S2: not_a

port map(

A=>S2,

C=>nS2

);

u3_not_S3: not_a

port map(

A=>S3,

C=>nS3

);

---3and---------------

u1_and_nS1nS2nS3: and3_abc

port map(

A=>nS1,

B=>nS2,

C=>nS3,

D=>sel1

);

u2_and_nS1nS2S3: and3_abc

port map(

A=>nS1,

B=>nS2,

C=>S3,

D=>sel2

);

u3_and_nS1S2nS3: and3_abc

port map(

A=>nS1,

B=>S2,

C=>nS3,

D=>sel3

);

u4_and_nS1S2S3: and3_abc

port map(

A=>nS1,

B=>S2,

C=>S3,

D=>sel4

);

u5_and_S1nS2nS3: and3_abc

port map(

A=>S1,

B=>nS2,

C=>nS3,

D=>sel5

);

u6_and_S1nS2S3: and3_abc

port map(

A=>S1,

B=>nS2,

C=>S3,

D=>sel6

);

u7_and_S1S2nS3: and3_abc

port map(

A=>S1,

B=>S2,

C=>nS3,

D=>sel7

);

------------------------

---and0---------------------

u1_and0: and_ab

port map

( A => sel1,

B => Din1(0),

C => tmp1(0)

);

u2_and0: and_ab

port map

( A => sel2,

B => Din2(0),

C => tmp2(0)

);

u3_and0: and_ab

port map

( A => sel3,

B => Din3(0),

C => tmp3(0)

);

u4_and0: and_ab

port map

( A => sel4,

B => Din4(0),

C => tmp4(0)

);

u5_and0: and_ab

port map

( A => sel5,

B => Din5(0),

C => tmp5(0)

);

u6_and0: and_ab

port map

( A => sel6,

B => Din6(0),

C => tmp6(0)

);

u7_and0: and_ab

port map

( A => sel7,

B => Din7(0),

C => tmp7(0)

);

------------------------

-----1-------------------

u1_and1: and_ab

port map

( A => sel1,

B => Din1(1),

C => tmp1(1)

);

u2_and1: and_ab

port map

( A => sel2,

B => Din2(1),

C => tmp2(1)

);

u3_and1: and_ab

port map

( A => sel3,

B => Din3(1),

C => tmp3(1)

);

u4_and1: and_ab

port map

( A => sel4,

B => Din4(1),

C => tmp4(1)

);

u5_and1: and_ab

port map

( A => sel5,

B => Din5(1),

C => tmp5(1)

);

u6_and1: and_ab

port map

( A => sel6,

B => Din6(1),

C => tmp6(1)

);

u7_and1: and_ab

port map

( A => sel7,

B => Din7(1),

C => tmp7(1)

);

------------------------

----2--------------------

u1_and2: and_ab

port map

( A => sel1,

B => Din1(2),

C => tmp1(2)

);

u2_and2: and_ab

port map

( A => sel2,

B => Din2(2),

C => tmp2(2)

);

u3_and2: and_ab

port map

( A => sel3,

B => Din3(2),

C => tmp3(2)

);

u4_and2: and_ab

port map

( A => sel4,

B => Din4(2),

C => tmp4(2)

);

u5_and2: and_ab

port map

( A => sel5,

B => Din5(2),

C => tmp5(2)

);

u6_and2: and_ab

port map

( A => sel6,

B => Din6(2),

C => tmp6(2)

);

u7_and2: and_ab

port map

( A => sel7,

B => Din7(2),

C => tmp7(2)

);

------------------------

----3--------------------

u1_and3: and_ab

port map

( A => sel1,

B => Din1(3),

C => tmp1(3)

);

u2_and3: and_ab

port map

( A => sel2,

B => Din2(3),

C => tmp2(3)

);

u3_and3: and_ab

port map

( A => sel3,

B => Din3(3),

C => tmp3(3)

);

u4_and3: and_ab

port map

( A => sel4,

B => Din4(3),

C => tmp4(3)

);

u5_and3: and_ab

port map

( A => sel5,

B => Din5(3),

C => tmp5(3)

);

u6_and3: and_ab

port map

( A => sel6,

B => Din6(3),

C => tmp6(3)

);

u7_and3: and_ab

port map

( A => sel7,

B => Din7(3),

C => tmp7(3)

);

------------------------

----4--------------------

u1_and4: and_ab

port map

( A => sel1,

B => Din1(4),

C => tmp1(4)

);

u2_and4: and_ab

port map

( A => sel2,

B => Din2(4),

C => tmp2(4)

);

u3_and4: and_ab

port map

( A => sel3,

B => Din3(4),

C => tmp3(4)

);

u4_and4: and_ab

port map

( A => sel4,

B => Din4(4),

C => tmp4(4)

);

u5_and4: and_ab

port map

( A => sel5,

B => Din5(4),

C => tmp5(4)

);

u6_and4: and_ab

port map

( A => sel6,

B => Din6(4),

C => tmp6(4)

);

u7_and4: and_ab

port map

( A => sel7,

B => Din7(4),

C => tmp7(4)

);

------------------------

--===========================

u1_or: or7_abc

port map

( A => tmp1(0),

B => tmp2(0),

C => tmp3(0),

D => tmp4(0),

E => tmp5(0),

F => tmp6(0),

G => tmp7(0),

H => Dout(0)

);

u2_or: or7_abc

port map

( A => tmp1(1),

B => tmp2(1),

C => tmp3(1),

D => tmp4(1),

E => tmp5(1),

F => tmp6(1),

G => tmp7(1),

H => Dout(1)

);

u3_or: or7_abc

port map

( A => tmp1(2),

B => tmp2(2),

C => tmp3(2),

D => tmp4(2),

E => tmp5(2),

F => tmp6(2),

G => tmp7(2),

H => Dout(2)

);

u4_or: or7_abc

port map

( A => tmp1(3),

B => tmp2(3),

C => tmp3(3),

D => tmp4(3),

E => tmp5(3),

F => tmp6(3),

G => tmp7(3),

H => Dout(3)

);

u5_or: or7_abc

port map

( A => tmp1(4),

B => tmp2(4),

C => tmp3(4),

D => tmp4(4),

E => tmp5(4),

F => tmp6(4),

G => tmp7(4),

H => Dout(4)

);

--=============================

end bhv;本回答被提问者采纳

linux权限管理快速上手

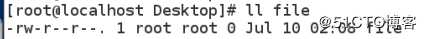

用ll或ls –l去查看目录下文件详细信息

第一位 文件类型 -

第二位 文件权限 rw-r--r--

第三位 硬链接数 1

第四位 文件的所有者 root

第五位 文件的所属组 root

第六位 文件大小 0

第七位 文件最后修改时间 Jul 10 02:08

文件类型

.- 二进制文件

B 块设备文件

C 字符设备文件

D 目录文件

L 软连接文件

P 管道符文件

S 套接字文件

文件三种权限

rwx详解:

r--:只读

-w-:写

--x:执行

数字表示:

?0 000 ---:无权限

?1 001 --x:执行

?2 010 -w-:写

?3 011 -wx:写和执行

?4 100 r--:只读

?5 101 r-x:读和执行

?6 110 rw-:读写

?7 111 rwx:读写执行

??

文件权限 数字表示 文件 目录

r 4 cat、head、vi查看文件内容 ls查看

w 2 echo修改添加内容到文件中 mkdir、touch创建

x 1 x执行权限,才能运行 cd打开此目录

用户三种权限

??1、文件的所有者:u?

??2、文件的所属群组:g?

??3、其他用户:o

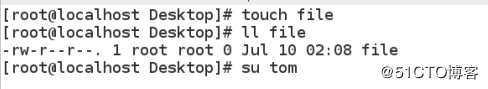

实验具体操作 --> 文件权限

创建文件file,使用ll命令查看file详细信息,切换到tom用户并系统环境不变

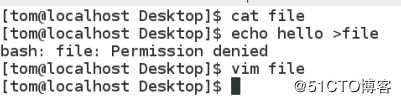

查看文件内容并添加hello内容到file文件,表示无写权限,用vim编辑file内容date命令,无写权限

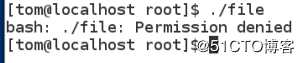

执行文件file,无执行权限,之上实验得出结论文件仅有只读权限

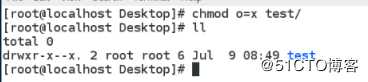

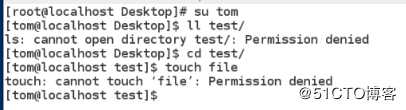

实验具体操作 --> 目录权限

创建目录test

变更目录的其他用户为仅有执行权限下明确实验目的,使用ll命令查看test详细信息

切换到tom用户并系统环境不变,使用ll命令查看test详细信息,表示无读权限

进入test目录,表示有执行权限,创建文件file,表示无写权限

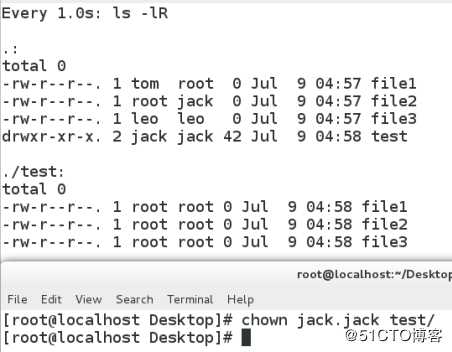

chown 修改文件或目录的所有者和所属组

-R 递归 将指定目录下的所有文件及子目录一并处理

chgrp 修改文件或目录的所属组

-R 递归 将指定目录下的所有文件及子目录一并处理

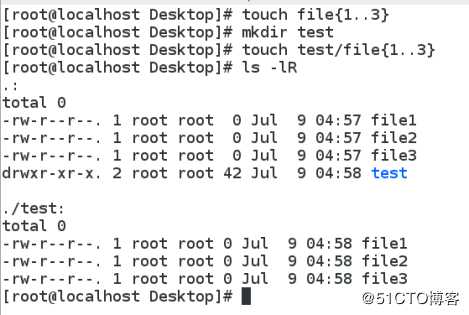

实验具体操作

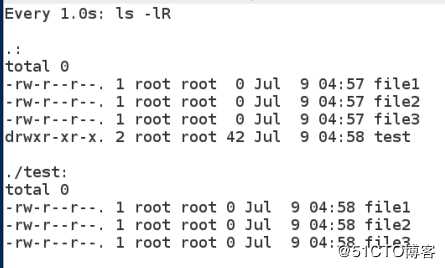

创建文件file1到file3,创建test目录,在目录test下创建文件file1到file3

使用ls -lR查看文件及目录和目录子文件详细信息

使用watch -n 1 ls -lR实时监控

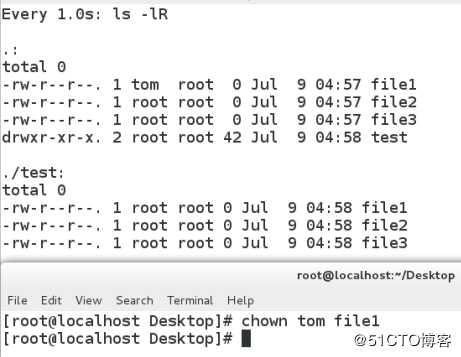

更改文件file1的属主为tom

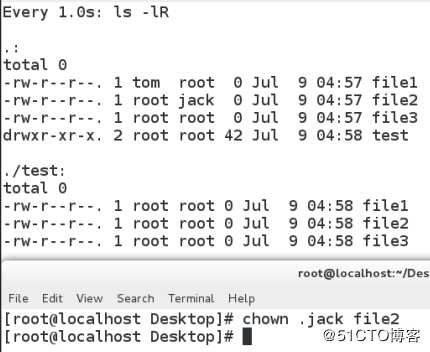

更改文件file2的属组jack

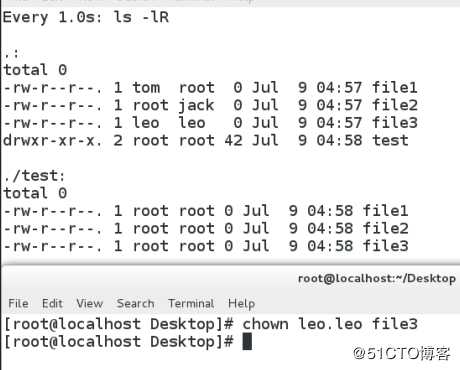

更改文件file3的属主及属组为leo

更改目录test的属主及属组为jack

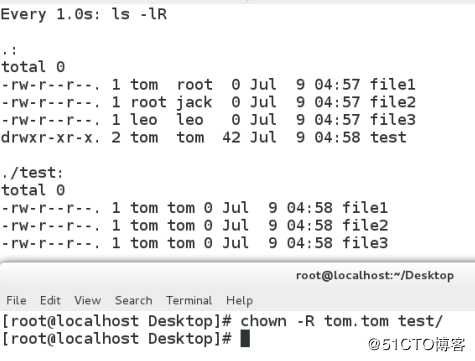

更改目录test并更改目录下文件的属主及属组为tom

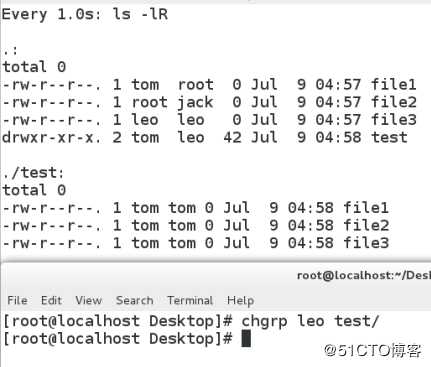

更改目录test属组为leo

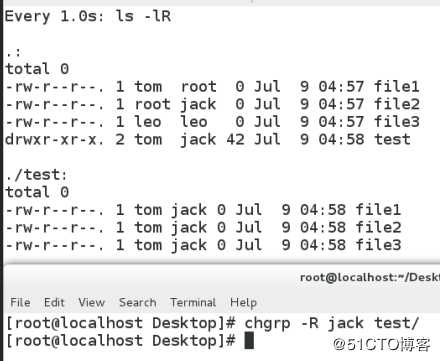

更改目录test并更改目录下文件属组为jack

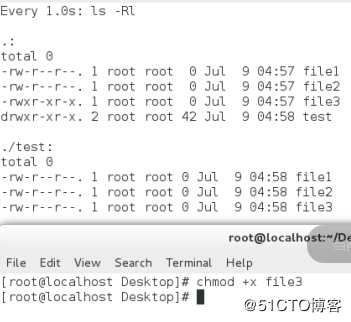

Chmod 功能修改文件权限

-R 递归 将指定目录下的所有文件及子目录一并处理

--reference 参考文件或目录 将源文件统统设置成目标文件的用户文件权限

修改文件权限有4种方法 :赋值法,加减法,数字法,替换法

实验具体操作

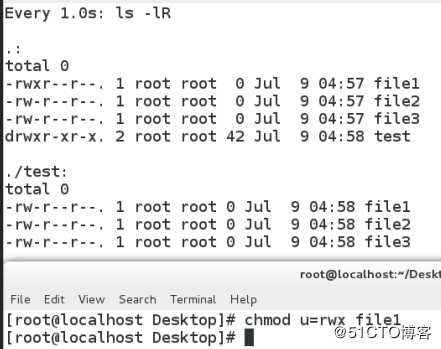

一 赋值法

更改文件file1所有者权限为读写执行

更改文件file2属主权限为只读,属组权限为读写执行

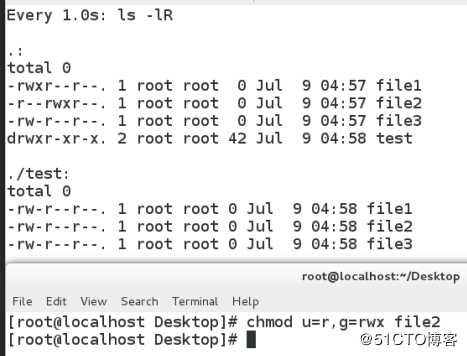

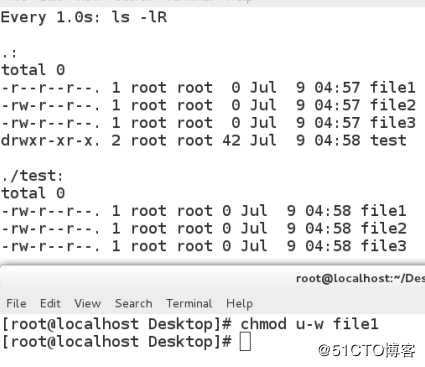

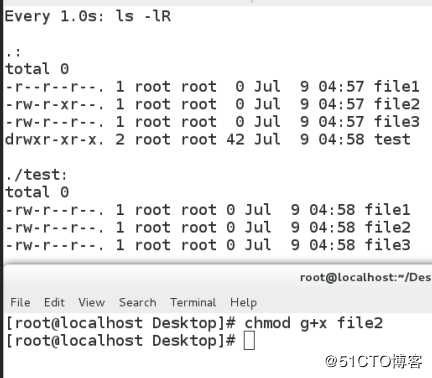

二 加减法

更改文件file1属主权限减去写权限

更改文件file2属组权限加执行权限

更改文件file3属主属组其他用户权限加执行权限

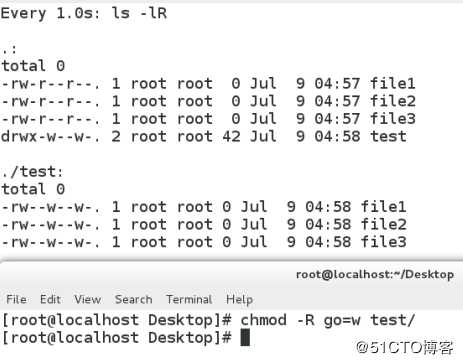

递归目录下子文件目录使用方法

更改目录test及目录下文件的属组和其他用户权限为写

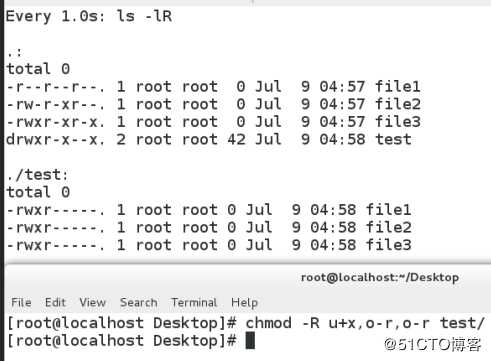

更改目录test及目录下文件属主加执行权限,属组减去读权限,其他用户减去读权限

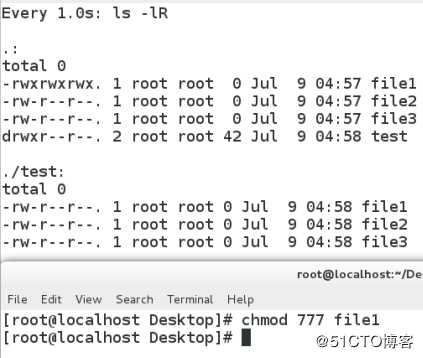

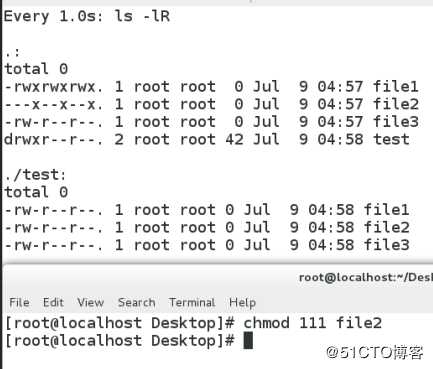

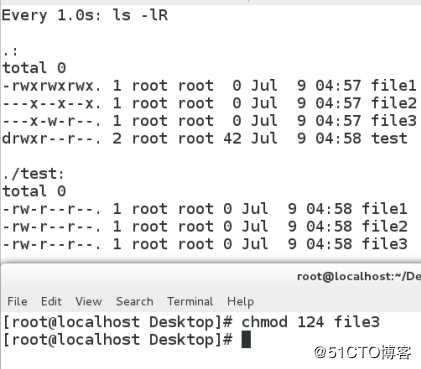

三 数字法

更改文件file1属主属组其他用户为读写执行权限

更改文件file1属主属组其他用户为执行权限

更改文件file3属主为执行权限,属组为写权限,其他用户为读权限

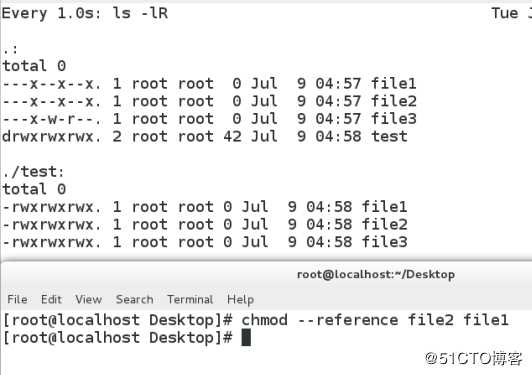

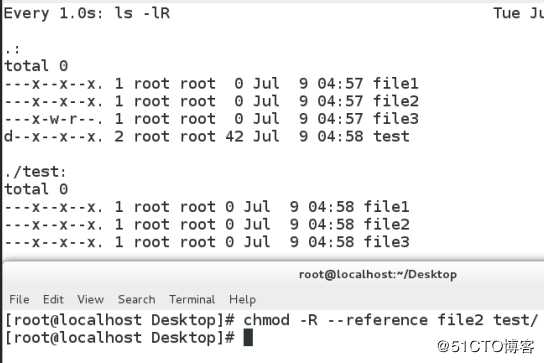

四 替换法

将文件file2权限替换给file1使用

将文件file2权限替换给目录test及目录下文件使用

以上是关于用VHDL写一个有七位(每个5bits)输入,三位控制信号的选择器。的主要内容,如果未能解决你的问题,请参考以下文章