用modelsim时报错,请大神指点,(主要看一下模块调用和参数配置的语法有问题吗?)

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了用modelsim时报错,请大神指点,(主要看一下模块调用和参数配置的语法有问题吗?)相关的知识,希望对你有一定的参考价值。

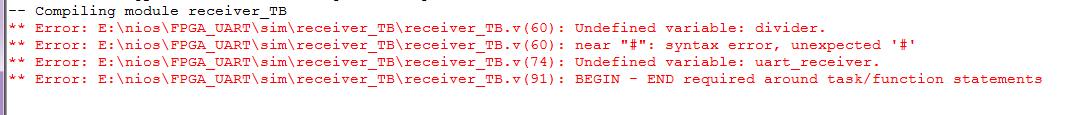

报错:一是Undefined variable: divider(没有定义模块),二是near "#": unexpected '#'(参数传递语法有问题),如图3。

一个verilog文件“divider”为分频模块,其中用了可配置参数,用来提供不同频率的时钟给串口接收模块。如图1。

一个是“uart_receiver”为串口接收模块,如图2,

在test_bench中调用者两个模块。

test_bench 如下:

`timescale 1ns/1ns

module receiver_TB;

reg clk,rst_n;

localparam PERIOD=20; //50MHz

initial

begin

clk=0;

forever #(PERIOD/2) clk=~clk;

end

//clk divider:9600bps

divider

#(

.DEVIDE_CNT(32'd824634)

)

u_divider2

(

.clk(clk),

.rst_n(rst_n),

.divide_clk(),

.divide_clken(divide_clken2)

);

//uart data txd simulated simulate

wire bps_en=divide_clken2;

reg fpga_rxd;

task task_uart_txd;

input [7:0] uart_data;

begin

@(posedge bps_en); fpga_rxd=0;

@(posedge bps_en); fpga_rxd=uart_data[0];

@(posedge bps_en); fpga_rxd=uart_data[1];

@(posedge bps_en); fpga_rxd=uart_data[2];

@(posedge bps_en); fpga_rxd=uart_data[3];

@(posedge bps_en); fpga_rxd=uart_data[4];

@(posedge bps_en); fpga_rxd=uart_data[5];

@(posedge bps_en); fpga_rxd=uart_data[6];

@(posedge bps_en); fpga_rxd=uart_data[7];

@(posedge bps_en); fpga_rxd=1;

#78;

end

endtask

task task_reset;

begin

rst_n=1;

#200;

rst_n=0;

#300;

rst_n=1;

end

//divider intantiation

divider #(.DEVIDE_CNT(32'd13194140))

u_divider

(

.clk(clk),

.rst_n(rst_n),

.divide_clk(),

.divide_clken(divide_clken)

);

wire clken_16bps=divide_clken;

//data receive from pc to fpga

wire rxd_flag;

wire [7:0] rxd_data;

uart_receiver u_uart_receiver

(

.clk (clk),

.rst_n (rst_n),

//input

.clken_16bps (clken_16bps),

.rxd (fpga_rxd),

//output

.rxd_flag (rxd_flag),

.rxd_data (rxd_data)

);

//system initialization

task task_sysinit;

begin

fpga_rxd=1;

end

endtask

initial

begin

task_sysinit;

task_reset;

#12345;

task_uart_txd(8'hCB);

#12345;

task_uart_txd(8'h0A);

#12345;

task_uart_txd(8'h09);

end

endmodule

final String user = "store";

final String password = "store_password";

Class.forName("oracle.jdbc.driver.OracleDriver");

Connection con = DriverManager.getConnection(url, user, password);

return con;

追问

什么意思啊

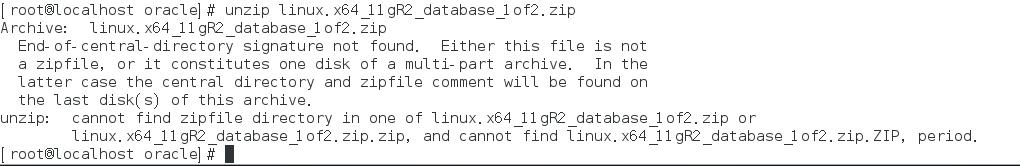

linux下用unzip解压时报错

报错内容如下:

求大神 解决。。

从你的文件名上看应该是两个分卷,那么你可以尝试:

cat 1.zip 2.zip > 0.zip

unzip 0.zip追问

不用的 我在别的 机子上 解压过

追答如果你在别的机器上能解开,那么你确实需要确认你的文件是否完整了。建议你比较可以解开的zip文件和无法解开的zip文件 的MD5是否一致

linux下可以直接输入:md5sum filename获得md5

以上是关于用modelsim时报错,请大神指点,(主要看一下模块调用和参数配置的语法有问题吗?)的主要内容,如果未能解决你的问题,请参考以下文章