ADC的ENOB的范围应该在ADC位数附近吗

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了ADC的ENOB的范围应该在ADC位数附近吗相关的知识,希望对你有一定的参考价值。

参考技术A 如何确定ADC的位数?Q1:

ADC位数是根据传输方式和噪声来计算的。如,64QAM/7/8码率在视频解码正常的最低信噪比为28dB(某种衰落信道下);OFDM在轻微削波时的峰均比假设为11dB,所以ADC的最大信噪比至少要40dB,考虑信号波动给AGC留出3dB的余量,那么ADC至少要42/6=7位。剩下的就应该是考虑到噪声等因素留的余量了。

ADC每增加一位,信噪比提高6dB,前提是输入ADC的波形没有噪声。模拟信号的信噪比是一定的,ADC之后的信号的最高信噪比也就定了。

我觉得得分情况。有两点:首先RF指标不可能无限高的;其次,RF指标越高成本越高。对低成本系统,是链路预算决定射频指标,如wlan;对高成本系统,可能是RF指标决定链路预算,如星际通信。

Q2:

选AD,看接收信号的动态范围要求和解调性能的要求。 非线性指标,取决于接收信号的特性以及干扰的特性。

ADC有效位数如何理解?

假设一个12位非理想的ADC,其ENOB为10bit,这并不表示把ADC的后两位删掉就可以当做一个理想的10bitADC来使用,如果去掉后两位把该ADC作为一个10bit的ADC来测试,你会发现它的ENOB不到10bit。

ENOB的计算方法是使用ADC测量出的SNDR根据公式SNDR=6.02*ENOB+1.76换算而来的,从这个公式我们可以明白这里ENOB的意思是12bit非理想ADC的SNDR与理想的10bitADC的SNR相等。

对于一个非理想的ADC,其输出不仅有量化噪声,还有失真引起的高次谐波,所以会在SNDR的计算中抵消一部分精度。

信噪失真比 SNDR:

SNDR是指频带内信号总功率和噪声以及谐波功率之和的比值。它的定义和SNR的定义类似,只是为了强调ADC中的谐波失真。

天天在用的ADC,内部原理你了解吗?

前言

用了这么久ADC,从没细看过ADC的内部原理和如何获得最佳精度,今天看到一篇ST的官方文档讲的不错,这里整理分享给大家。

SAR ADC内部结构

STM32微控制器中内置的ADC使用SAR(逐次逼近)原则,分多步执行转换。转换步骤数等 于ADC转换器中的位数。每个步骤均由ADC时钟驱动。每个ADC时钟从结果到输出产生一 位。ADC的内部设计基于切换电容技术。下面的图介绍了ADC的工作原理。下面的示例仅显示了逼近的前面几步,但是该过程会持续到LSB为止

SAR切换电容ADC的基本原理(10位ADC示例)

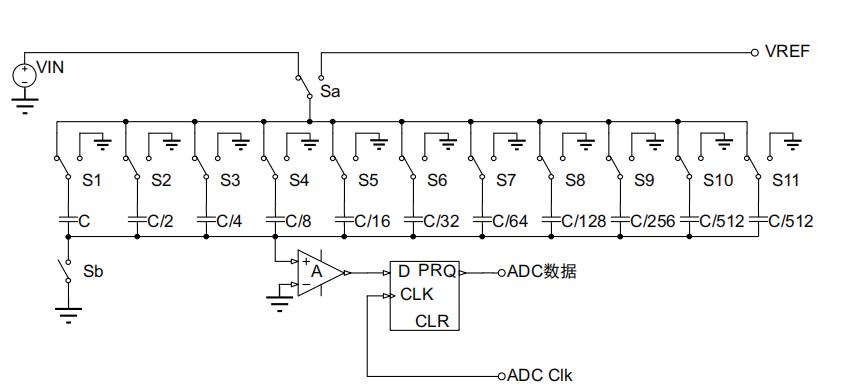

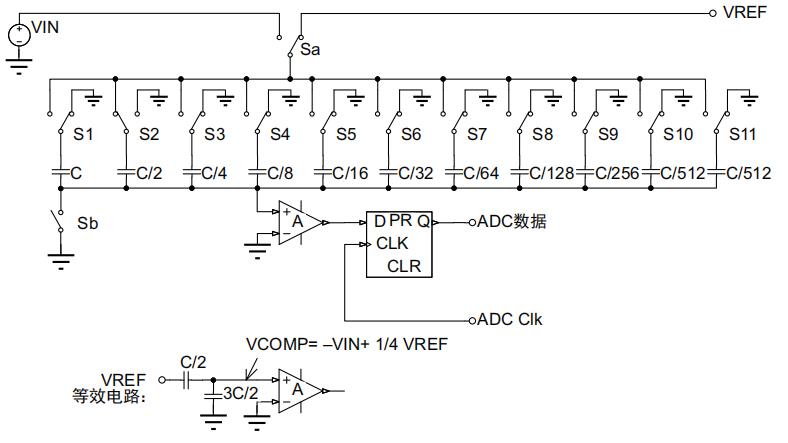

带数字输出的ADC基本原理图

采样状态

采样状态:电容充电至电压VIN。Sa切换至VIN,采样期间Sb开关闭合

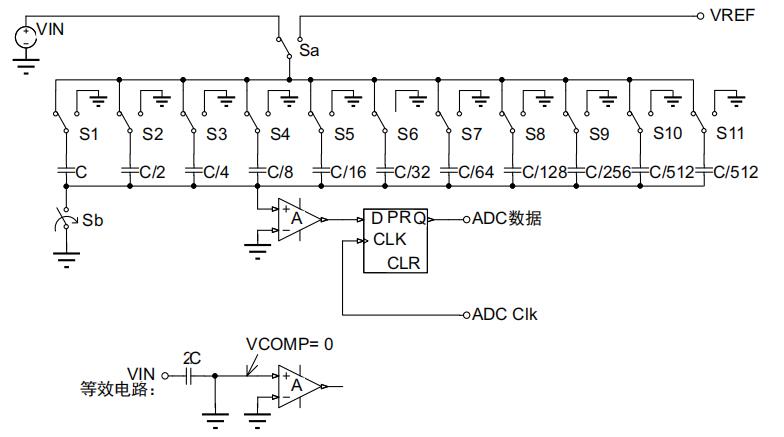

保持状态

保持状态:输入断开,电容保持输入电压。Sb开关打开,然后S1-S11切换至接地且Sa切换至VREF。

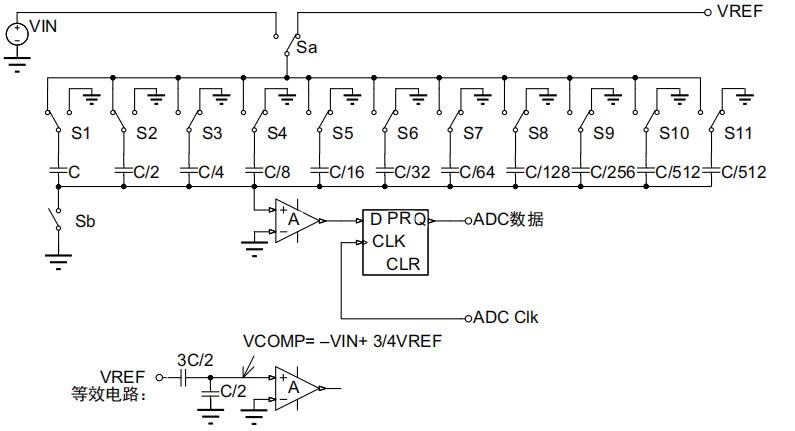

逐次逼近

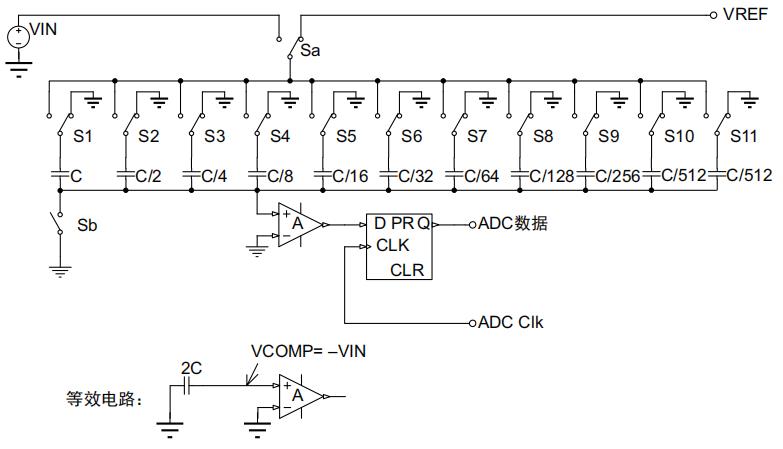

1、第一个逼近步骤。S1切换至VREF。VIN与VREF/2比较

2、如果MSB = 0,则与¼VREF进行比较,S1切换回接地。S2切换至VREF。

3、如果MSB = 1,则与¾VREF进行比较,S1保持接地。S2切换至VREF。

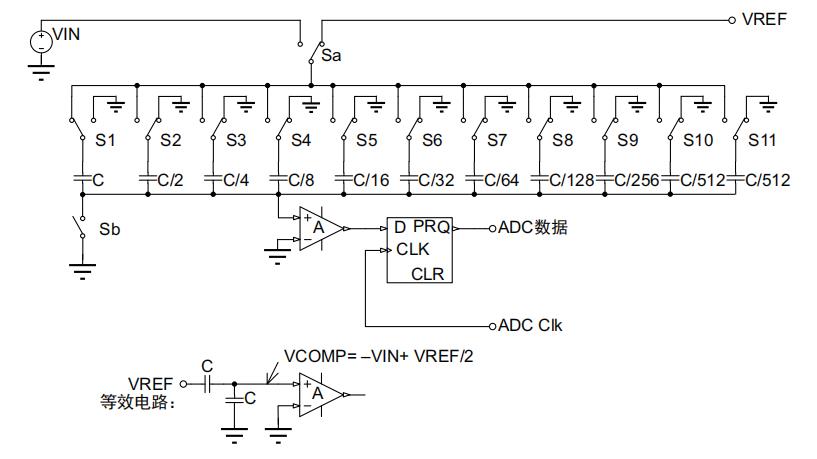

重复如上步骤,直到LSB为止。可以简单理解为二分法逐次进行输入电压与参考电压的比较。首次于VREF/2比较,下次比较根据上次比较结果决定,如果MSB=1则与¾VREF比较。如果MSB=0则与¼VREF比较。后面决定与1/8VREF 3/8VREF、 5/8VREF、 7/8VREF之一做比较。循环直到输出LSB为止。

以上是关于ADC的ENOB的范围应该在ADC位数附近吗的主要内容,如果未能解决你的问题,请参考以下文章