如何使用3线-8线译码器和各种数字集成电路构成一个2线-4线译码器??????请画出电路图!!!!

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了如何使用3线-8线译码器和各种数字集成电路构成一个2线-4线译码器??????请画出电路图!!!!相关的知识,希望对你有一定的参考价值。

如何使用3线-8线译码器和各种数字集成电路构成一个2线-4线译码器??????请画出电路图!!!!!

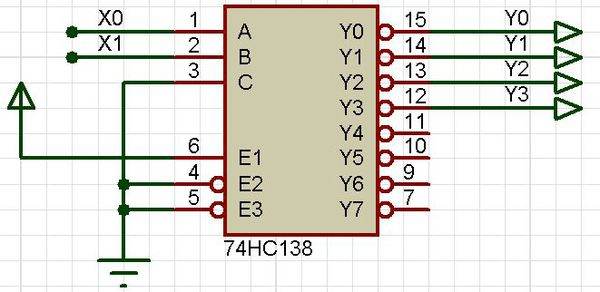

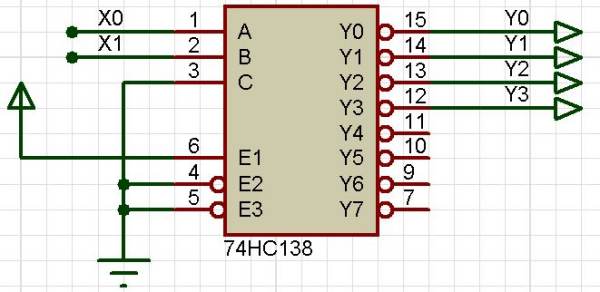

选择一片74HC138,因为输入信号是高电平有效,要实现2线-4线译码器,可以直接将高输入位悬空或接低电平;输出端直接选择低四位,高四位可以选择悬空;最后使能输入端按74HC138正常连接即可,具体见下图:

注:74HC138是低电平输入有效,只需要在低四位输出端上接上非门即可。

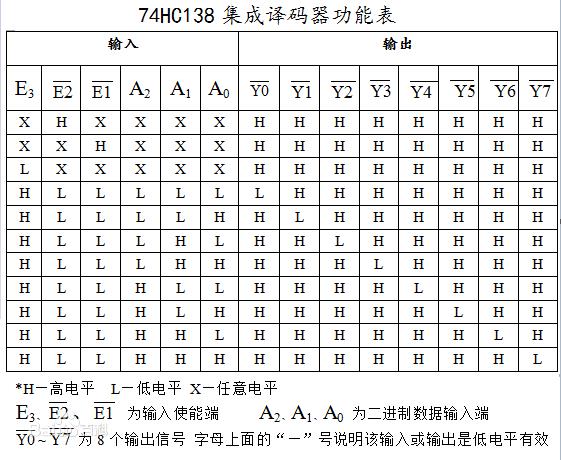

附74HC138功能表如下:

输出Y0~Y3,低电平有效

如果需要高电平输出,则每一输出端加接一非门(反相器)即可

追问我想问下 E1端连接的倒置三角形什么意思?还有输出端Y4Y5Y6Y7只是漏出个线头不用管了么???

追答最前面的三角形是电源正极;E3下面的是电源负极。

3-8线比2-4线更多,用不完,闲着不用。

输出Y5~Y7可以空着,但输入端C必须接合适的电平。

厉害啊 真心佩服 以后我不会的还要向你请教 希望你可以帮助我 谢谢

追答不谢

本回答被提问者和网友采纳数字电路实验(04)中规模组合逻辑电路实验3:译码器及其应用

数字电路实验(04)中规模组合逻辑电路实验3:译码器及其应用

2020-5-23

一.实验要求

1.1.实验目的

- 认识译码器的定义、功能及基本使用;

- 熟悉译码器(74HC138)的功能和级联。

1.2.实验器材

- VCC

- Ground

- 3线-8线反相译码器74HC138

- 指示灯

1.3.实验内容

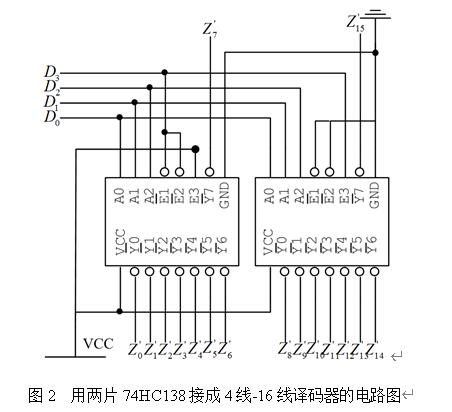

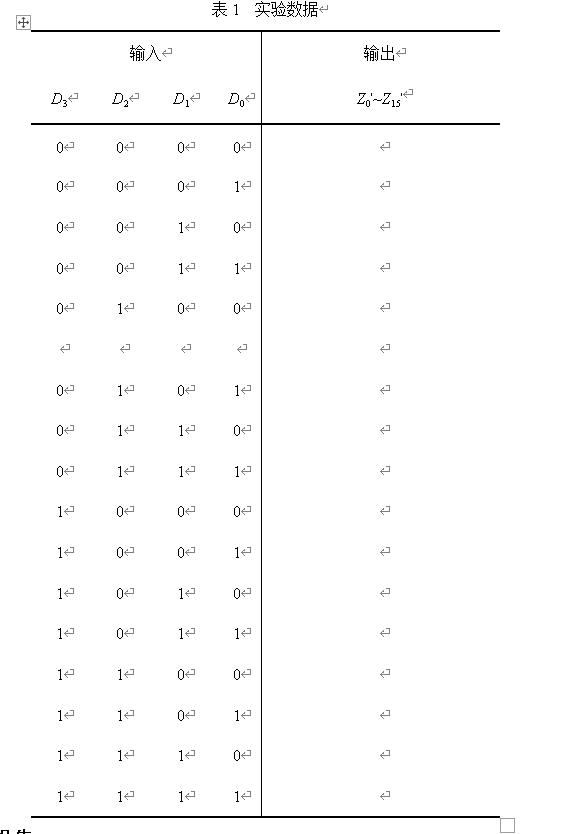

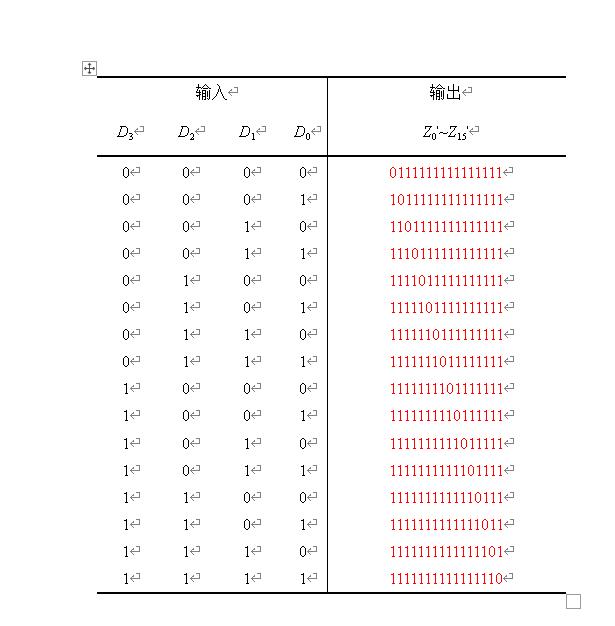

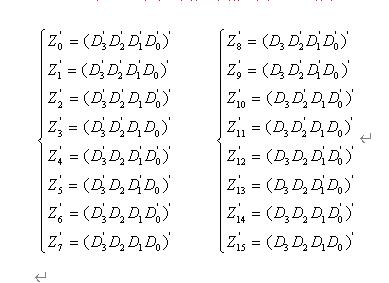

利用两片3线-8线译码器74HC138组成4线-16线译码器,要求:将输入的4位二进制代码D3D2D1D0译成16个独立的低电平信号Z0’~Z15’。

1.4.实验原理

- 译码器

译码器(Decoder)的逻辑功能是将每个输入的二进制代码译成对应的输出高、低电平信号或另外一个代码。因此,译码是编码的反操作。常用的译码器电路有二进制译码器、二-十进制译码器和显示译码器三类。 - 74HC138

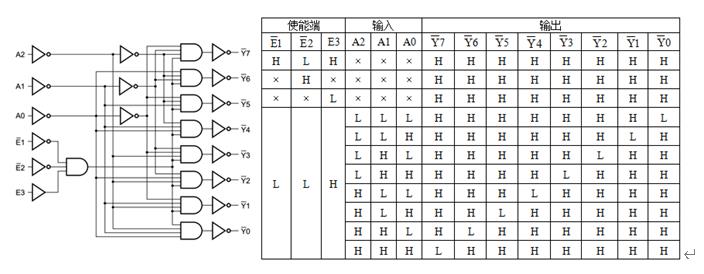

74HC138是用CMOS门电路组成的3线-8线译码器,该译码器可接受3位二进制加权地址输入(A0,A1和A2),并当使能时,提供8个互斥的低有效输出(Y0’~Y7’)。74HC138特有3个使能输入端:两个低有效(E1’和E2’)和一个高有效(E3)。除非E1’和E2’置低且E3置高,否则74HC138将保持所有输出为高。74HC138逻辑图及真值表信息如图1所示。

根据74HC138真值表得出,当E1’和E2’置低且E3置高时,输入和输出之间的逻辑函数式为:Y0’=(A2’A1’A0’)’,Y1’=(A2’A1’A0)’,Y2’=(A2’A1A0’)’,Y3’=(A2’A1A0)’,Y4’=(A2A1’A0’)’,Y5’=(A2A1’A0)’,Y6’=(A2A1A0’)’,Y7’=(A2A1A0)’。

二.实验图

三.实验报告内容

3.1.实验内容及步骤

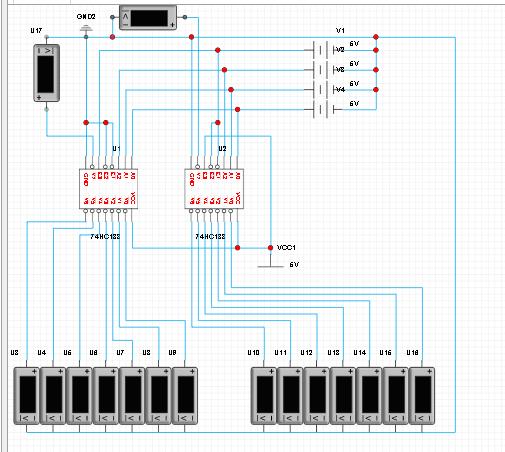

利用数字芯片74HC138接成4线-16线译码器,具体实验电路步骤如下所示:

- 令两片74HC138的输入端A2=D2,A1=D1,A0=D0;取第1片74HC138的E1’和E2’作为第四个地址输入端D3,并将其连接到第2片74HC138的E3端;

- 令第1片74HC138的控制端E3=1,第2片74HC138的控制端E1’=E2’=0(参考图2);

- 将输出端Z接入指示灯。D0~D3端接直流信号源(如VCC)。规定:输入端逻辑“1”与电压值“5V”对应,逻辑“0”与电压值“0V”对应;输出端“灯亮”与逻辑“1”对应,“灯灭”与逻辑“0”对应;

- 根据表1中D0~D3的逻辑值改变相应的输入状态,运行实验,观察输入端和输出之间的状态关系,记录相应的输出于表1中。

3.2.实验报告

- 搭建实验电路完成实验,补充完整表1;

- 写出4线-16线译码器的输出表达式。

以上是关于如何使用3线-8线译码器和各种数字集成电路构成一个2线-4线译码器??????请画出电路图!!!!的主要内容,如果未能解决你的问题,请参考以下文章

数字电路实验(04)中规模组合逻辑电路实验3:译码器及其应用

如何用双2-4线译码器转换为3-8线译码器?电路图怎么设计?