6713与FPGA连接时EMIF中的CECTL寄存器如何设置?

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了6713与FPGA连接时EMIF中的CECTL寄存器如何设置?相关的知识,希望对你有一定的参考价值。

6713通过写地址单元向FPGA中发送数据,FPGA根据此地址把数据放在相应的寄存器里,读过程相反,没有通过FIFO传输,请问这时EMIF中的CECTL寄存器如何设置?我知道把FPGA看作异步接口来设置,如异步SRAM的设置可以通过SRAM芯片手册中的时序参数设置CECTL寄存器,但是在FPGA芯片手册中没有像SRAM那样的时序图和参数,所以就不知道该怎么设置了。在论坛里搜索了但没找到具体的设置方法,所以发帖求助,望高手解答,谢谢!

DSP配置成SRAM接口,在FPGA部分只要把地址线对应的数据传输就行了 参考技术A 建立、选通、保持时间,不同厂商的FPGA应该会有差异,要根据EMIF的时钟以及实际调试来确定TMS320DM642的emif(外部存储器接口)的设置结构

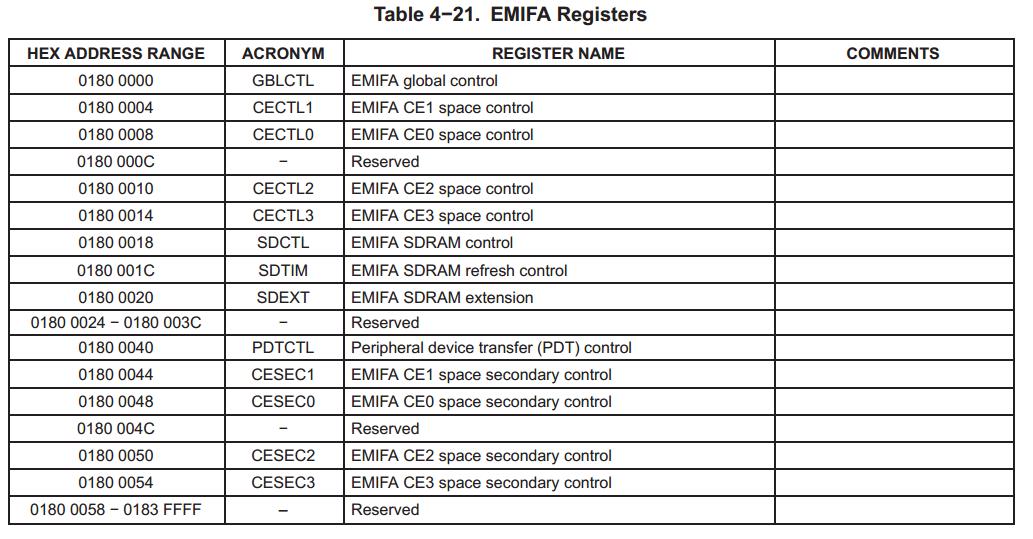

EMIF中存在一组存储器映射寄存器,如下图所示,通过设置这些寄存器来完成对EMIF的控制,包括配置各个空间的存储器类型,设置相应的接口时序等。

EMIFA 寄存器

EMIF全局控制寄存器(GBLCTL)

CE空间控制寄存器(CECTL)

CE空间控制寄存器(CECTL)与EMIF支持的CE存储器空间相关。C6000 DSP具有与4个外部CE信号相关的4个CE空间控制寄存器。

SDRAM控制寄存器(SDCTL)

SDRAM控制寄存器(SDCTL)控制用于所有CE空间的SDRAM参数,CE空间通过该寄存器的MTYPE位段指定一个SDRAM存储器类型。因为SDCTL控制所有SDRAM空间,每个空间必须包含具有相同的刷新、时序和页面属性。当访问SDRAM时,SDCTL不能被修改。

SDRAM时序寄存器(SDTIM)

SDRAM扩展寄存器(SDEXT)

CE空间从控制寄存器(CExSEC)

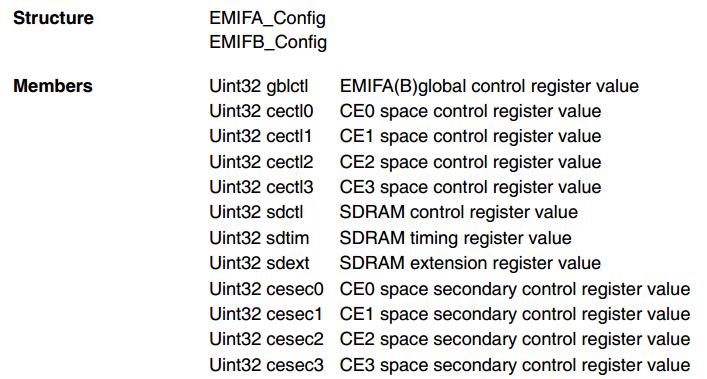

EMIFA外设结构 配置

EMIFA_Config vmd642ConfigA ={ //设置EMIFA外设的结构 0x00052078,/*gblctl EMIFA(B)global control register value */ /*将CLK6、4、1使能;将MRMODE置1;使能EK2EN,EK2RATE*/ 0xffffffd3,/*cectl0 CE0 space control register value*/ /*将CE0空间设为SDRAM*/ 0x73a28e01,/*cectl1 CE1 space control register value*/ /*Read hold: 1 clock; MTYPE : 0000,选择8位的异步接口 Read strobe :001110;14个clock宽度 TA:2 clock; Read setup 2 clock; Write hold :2 clock; Write strobe: 14 clock Write setup :7 clock -- --------------- \\ 14c /1c \\----------------/ */ 0x22a28a22, /*cectl2 CE2 space control register value*/ 0x22a28a42, /*cectl3 CE3 space control register value*/ 0x57115000, /*sdctl SDRAM control register value*/ 0x0000081b, /*sdtim SDRAM timing register value*/ 0x001faf4d, /*sdext SDRAM extension register value*/ 0x00000002, /*cesec0 CE0 space secondary control register value*/ 0x00000002, /*cesec1 CE1 space secondary control register value*/ 0x00000002, /*cesec2 CE2 space secondary control register value*/ 0x00000073 /*cesec3 CE3 space secondary control register value*/ };

以上是关于6713与FPGA连接时EMIF中的CECTL寄存器如何设置?的主要内容,如果未能解决你的问题,请参考以下文章